# ACPL-M60L High Speed LVTTL Compatible 3.3 Volt Optocouplers

# **Data Sheet**

### Description

The ACPL-M60L is an optically coupled gate that combines a GaAsP light emitting diode and an integrated high gain photo detector. The output of the detector IC is an open collector Schottky-clamped transistor. The internal shield provides a guaranteed common mode transient immunity specification of 15 kV/ $\mu$ s.

This unique design provides maximum AC and DC circuit isolation while achieving LVTTL/LVCMOS compatibility. The optocoupler AC and DC operational parameters are guaranteed from  $-40^{\circ}$ C to  $+85^{\circ}$ C, allowing trouble-free system performance.

These optocouplers are suitable for high speed logic interfacing, input/output buffering, as line receivers in environments that conventional line receivers cannot tolerate and are recommended for use in extremely high ground or induced noise environments.

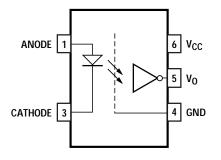

### **Functional Diagram**

#### Features

- · Low power consumption

- + 15 kV/ $\mu s$  minimum Common Mode Rejection (CMR) at  $V_{\mbox{\tiny CM}}$  = 1000 V

- High speed: 15 MBd typical

- LVTTL/LVCMOS compatible

- · Low input current capability: 5 mA

- Guaranteed AC and DC performance over temperature:  $-40\,^\circ\text{C}$  to  $+85\,^\circ\text{C}$

- Safety approvals; UL, CSA, IEC/EN/DIN EN 60747-5-2 (pending)

- · Surface mountable

- Very small, low profile JEDEC Registered package outline

#### Applications

- · Isolated line receiver

- · Computer-peripheral interfaces

- · Microprocessor system interfaces

- Digital isolation for A/D, D/A conversion

- Switching power supply

- Instrument input/output isolation

- Ground loop elimination

- Pulse transformer replacement

- Field buses

CAUTION: It is advised that normal static precautions be taken in handling and assembly of this component to prevent damage and/or degradation which may be induced by ESD.

# **Ordering Information**

ACPL-M60L-000E (Tube package of 100 units, lead-free option) ACPL-M60L-500E (Tape and Reel package of 1500 units, lead-free option)

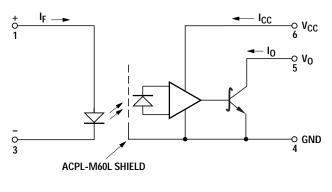

### Schematic

USE OF A 0.1 µF BYPASS CAPACITOR MUST BE CONNECTED BETWEEN PINS 6 AND 4 (SEE NOTE 1).

| TRUTH TABLE<br>(POSITIVE LOGIC) |        |  |  |  |  |  |  |

|---------------------------------|--------|--|--|--|--|--|--|

| LED                             | OUTPUT |  |  |  |  |  |  |

| ON L                            |        |  |  |  |  |  |  |

| OFF H                           |        |  |  |  |  |  |  |

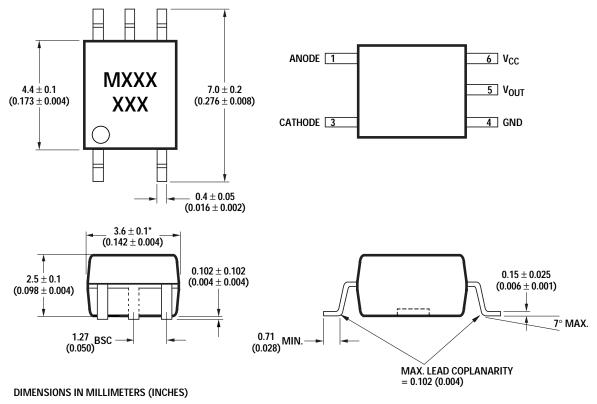

#### Package Outline Drawing

\* MAXIMUM MOLD FLASH ON EACH SIDE IS 0.15 mm (0.006)

NOTE: FLOATING LEAD PROTRUSION IS 0.15 mm (6 mils) MAX.

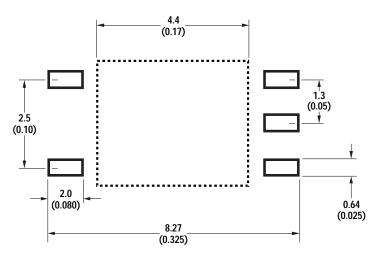

Land Pattern

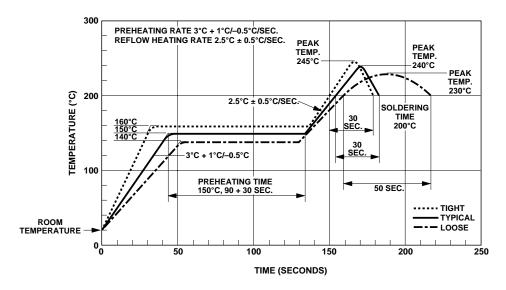

#### Solder Reflow Temperature Profile

Note: Use of non chlorine-activated fluxes is highly recommended.

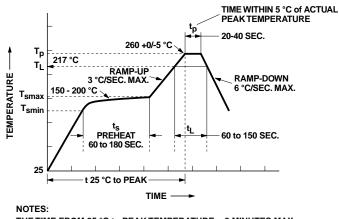

#### **Recommended PB-Free IR Profile**

THE TIME FROM 25 °C to PEAK TEMPERATURE = 8 MINUTES MAX. Tsmax = 200 °C, Tsmin = 150 °C

Note: Use of non chlorine-activated fluxes is highly recommended.

#### Parameter Symbol Value Units Conditions Minimum External Air Gap L (101) ≥5 Measured from input terminals to output mm (Clearance) terminals Minimum External Tracking Path L (102) ≥5 Measured from input terminals to output mm (Creepage) terminals 0.08 Minimum Internal Plastic Gap Through insulation distance, conductor to mm

CTI

175

Illa

V

conductor

DIN IEC 112/VDE 0303 Part 1

Material Group DIN VDE 0109

#### Insulation and Safety Related Specifications

4

(Clearance)

**Tracking Resistance**

Isolation Group (per DIN VDE 0109)

# Absolute Maximum Ratings (No Derating Required up to 85°C)

| Parameter                          | Symbol          | Min.      | Max.            | Units        | Note |

|------------------------------------|-----------------|-----------|-----------------|--------------|------|

| Storage Temperature                | Ts              | -55       | 125             | °C           |      |

| Operating Temperature†             | T <sub>A</sub>  | -40       | 85              | °C           |      |

| Average Forward Input Current      | IF              |           | 20              | mA           | 1    |

| Reverse Input Voltage              | V <sub>R</sub>  |           | 5               | V            |      |

| Input Power Dissipation            | Pl              |           | 40              | mW           |      |

| Supply Voltage (1 minute maximum)  | V <sub>CC</sub> |           | 7               | V            |      |

| Output Collector Current           | lo              |           | 50              | mA           |      |

| Output Collector Voltage           | Vo              |           | 7               | V            |      |

| Output Collector Power Dissipation | P <sub>0</sub>  |           | 85              | mW           |      |

| Solder Reflow Temperature Profile  |                 | See Packa | ige Outline Dra | wings sectio | n    |

# **Recommended Operating Conditions**

| Parameter                                      | Symbol             | Min. | Max. | Units     |

|------------------------------------------------|--------------------|------|------|-----------|

| Input Current, Low Level                       | I <sub>FL</sub> *  | 0    | 250  | μA        |

| Input Current, High Level <sup>[1]</sup>       | I <sub>FH</sub> ** | 5    | 15   | mA        |

| Power Supply Voltage                           | V <sub>CC</sub>    | 2.7  | 3.6  | V         |

| Operating Temperature                          | T <sub>A</sub>     | -40  | 85   | °C        |

| Fan Out (at $R_L = 1 k\Omega$ ) <sup>[1]</sup> | Ν                  |      | 5    | TTL Loads |

| Output Pull-up Resistor                        | RL                 | 330  | 4 k  | Ω         |

|                                                |                    |      |      |           |

\*The off condition can also be guaranteed by ensuring that V<sub>FL</sub>  $\leq$  0.8 volts. \*\*The initial switching threshold is 5 mA or less. It is recommended that 6.3 mA to 10 mA be used for best performance and to permit at least a 20% LED degradation guardband.

# **Electrical Specifications**

Over Recommended Temperature ( $T_A = -40^{\circ}C$  to  $+85^{\circ}C$ ) unless otherwise specified. All Typicals at V<sub>CC</sub> = 3.3 V,  $T_A = 25^{\circ}C$ .

| Parameter                                 | Sym.                      | Min. | Тур. | Max.  | Units | Test Conditions                                                     | Fig. | Note |

|-------------------------------------------|---------------------------|------|------|-------|-------|---------------------------------------------------------------------|------|------|

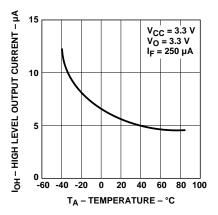

| High Level<br>Output Current              | I <sub>OH</sub> *         |      | 4.5  | 50    | μA    | $V_{CC} = 3.3 V,$<br>$V_0 = 3.3 V, I_F = 250 \mu A$                 | 1    |      |

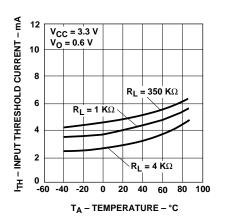

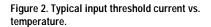

| Input Threshold<br>Current                | I <sub>TH</sub>           |      | 3.0  | 5.0   | mA    | $V_{CC} = 3.3 V,$<br>$V_{O} = 0.6 V,$<br>$I_{OL}$ (Sinking) = 13 mA | 2    |      |

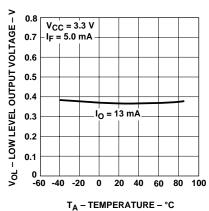

| Low Level<br>Output Voltage               | V <sub>OL</sub> *         |      | 0.35 | 0.6   | V     | $V_{CC} = 3.3 V,$<br>$I_F = 5 mA,$<br>$I_{OL}$ (Sinking) = 13 mA    | 3    |      |

| High Level<br>Supply Current              | I <sub>CCH</sub>          |      | 4.7  | 7.0   | mA    | I <sub>F</sub> = 0 mA<br>V <sub>CC</sub> = 3.3 V                    |      |      |

| Low Level<br>Supply Current               | I <sub>CCL</sub>          |      | 7.0  | 10.0  | mA    | I <sub>F</sub> = 10 mA<br>V <sub>CC</sub> = 3.3 V                   |      |      |

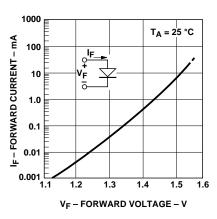

| Input Forward<br>Voltage                  | V <sub>F</sub>            | 1.4  | 1.5  | 1.75* | V     | $T_{A} = 25^{\circ}C, I_{F} = 10 \text{ mA}$                        | 5    |      |

| Input Reverse<br>Breakdown<br>Voltage     | BV <sub>R</sub> *         | 5    |      |       | V     | I <sub>R</sub> = 10 μA                                              |      |      |

| Input Diode<br>Temperature<br>Coefficient | $\Delta V_F / \Delta T_A$ |      | -1.6 |       | mV°C  | I <sub>F</sub> = 10 mA                                              |      |      |

| Input<br>Capacitance                      | C <sub>IN</sub>           |      | 60   |       | pF    | $f = 1 MHz, V_F = 0 V$                                              |      |      |

\*The JEDEC Registration specifies 0°C to +70°C. Avago specifies -40°C to +85°C.

#### Switching Specifications

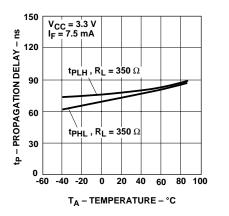

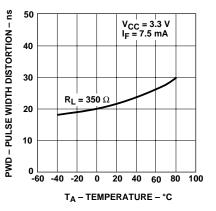

Over Recommended Temperature ( $T_A = -40^{\circ}C$  to +85°C),  $V_{CC} = 3.3$  V,  $I_F = 7.5$  mA unless otherwise specified. All Typicals at  $T_A = 25^{\circ}C$ ,  $V_{CC} = 3.3$  V.

| Parameter                                         | Sym.                                | Min. | Тур. | Max. | Units | Test Conditions                                                            | Fig.  | Note |

|---------------------------------------------------|-------------------------------------|------|------|------|-------|----------------------------------------------------------------------------|-------|------|

| Propagation Delay<br>Time to High Output<br>Level | t <sub>PLH</sub>                    |      |      | 90   | ns    | $ \begin{array}{l} R_{L} = 350 \; \Omega \\ C_{L} = 15 \; pF \end{array} $ | 6,7,8 | 5    |

| Propagation Delay<br>Time to Low Output<br>Level  | t <sub>PHL</sub>                    |      |      | 75   | ns    |                                                                            |       | 6    |

| Pulse Width<br>Distortion                         | t <sub>PHL</sub> – t <sub>PLH</sub> |      |      | 25   | ns    |                                                                            | 8     | 8    |

| Propagation Delay<br>Skew                         | t <sub>PSK</sub>                    |      |      | 40   | ns    |                                                                            |       |      |

| Output Rise Time<br>(10-90%)                      | tr                                  |      | 45   |      | ns    |                                                                            |       |      |

| Output Fall Time<br>(90-10%)                      | t <sub>f</sub>                      |      | 20   |      | ns    |                                                                            |       |      |

\*JEDEC registered data for the 6N137.

| Parameter                                             | Sym.            | Device    | Min.   | Тур.   | Units | Test Conditions            |                                                                                                                                                                                                                 | Fig. | Note   |

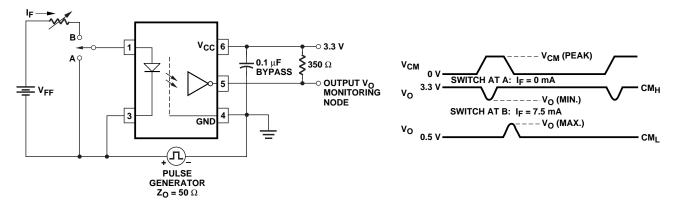

|-------------------------------------------------------|-----------------|-----------|--------|--------|-------|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------|

| Logic High<br>Common<br>Mode<br>Transient<br>Immunity | CM <sub>H</sub> | ACPL-M60L | 15,000 | 25,000 | V/µs  | V <sub>CM</sub>   = 1000 V |                                                                                                                                                                                                                 | 9    | 9, 11  |

| Logic Low<br>Common<br>Mode<br>Transient<br>Immunity  | CM <sub>L</sub> | ACPL-M60L | 15,000 | 25,000 | V/µs  | V <sub>CM</sub>   = 1000 V | $\label{eq:V_CC} \begin{array}{l} V_{CC} = 3.3 \ \text{V}, \ \text{I}_{\text{F}} = 7.5 \ \text{mA}, \\ V_{O(MAX)} = 0.8 \ \text{V}, \\ R_{L} = 350 \ \Omega, \ \text{T}_{\text{A}} = 25 \ \text{C} \end{array}$ | 9    | 10, 11 |

Notes:

- 1. Peaking circuits may produce transient input currents up to 50 mA, 50 ns maximum pulse width, provided average current does not exceed 20 mA.

- 2. Peaking circuits may produce transient input currents up to 50 mA, 50 ns maximum pulse width, provided average current does not exceed 15 mA.

- 3. Derate linearly above +80°C free-air temperature at a rate of 2.7 mW/°C for the SOIC-8 package.

- 4. Bypassing of the power supply line is required, with a 0.1 µF ceramic disc capacitor adjacent to each optocoupler.

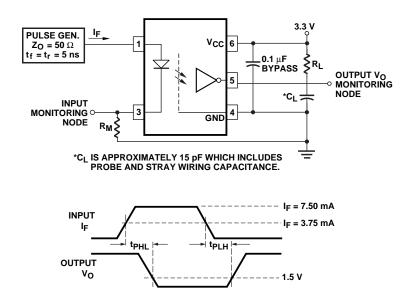

Total lead length between both ends of the capacitor and the isolator pins should not exceed 20 mm. 5. The t<sub>PLH</sub> propagation delay is measured from the 3.75 mA point on the falling edge of the input pulse to the 1.5 V point on the rising edge of the output pulse.

6. The t<sub>PHL</sub> propagation delay is measured from the 3.75 mA point on the rising edge of the input pulse to the 1.5 V point on the falling edge of the output pulse.

7. t<sub>PSK</sub> is equal to the worst case difference in t<sub>PHL</sub> and/or t<sub>PLH</sub> that will be seen between units at any given temperature and specified test conditions.

8. See test circuit for measurement details.

9.  $CM_H$  is the maximum tolerable rate of rise on the common mode voltage to assure that the output will remain in a high logic state (i.e.,  $V_0 > 2.0$  V).

10.  $CM_L$  is the maximum tolerable rate of fall of the common mode voltage to assure that the output will remain in a low logic state (i.e.,  $V_0 < 0.8$  V).

11. For sinusoidal voltages,  $(|dV_{CM}| / dt)_{max} = \pi f_{CM}V_{CM}$  (p-p).

Figure 1. Typical high level output current vs. temperature.

Figure 3. Typical low level output voltage vs. temperature.

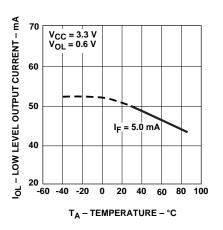

Figure 4. Typical low level output current vs. temperature.

Figure 5. Typical input diode forward characteristic.

Figure 6. Test circuit for tPHL and tPLH.

Figure 7. Typical propagation delay vs. temperature.

Figure 8. Typical pulse width distortion vs. temperature.

Figure 9. Test circuit for common mode transient immunity and typical waveforms.

For product information and a complete list of distributors, please go to our website: www.avagotech.com

Avago, Avago Technologies, and the A logo are trademarks of Avago Technologies Limited in the United States and other countries. Data subject to change. Copyright © 2006 Avago Technologies Limited. All rights reserved. AV01-0273EN June 26, 2006