### **Features**

- Operating voltage: 2.5V~5.5V

- Minimal external components

- · No external filter is required

- Low standby current (on power down mode)

- · Excellent performance

- Tristate data output for MCU interface

- · 3.58MHz crystal or ceramic resonator

- 1633Hz can be inhibited by the INH pin

# **General Description**

The XD/XL9170 are Dual Tone Multi Frequency (DTMF) receivers integrated with digital decoder and bandsplit filter functions as well as power-down mode and inhibit mode operations. Such devices use digital counting techniques to detect and decode all the 16 DTMF tone pairs into a 4-bit code output.

Highly accurate switched capacitor filters are implemented to divide tone signals into low and high group signals. A built-in dial tone rejection circuit is provided to eliminate the need for pre-filtering.

### Ordering information

| Ordering Information |         |         |              |                  |      |           |          |  |  |

|----------------------|---------|---------|--------------|------------------|------|-----------|----------|--|--|

| part                 | Device  | Package | Body size    | Temperature (°C) | MSL  | Transport | Package  |  |  |

| Number               | Marking | type    | (mm)         | remperature (C)  | WOL  | Media     | Quantity |  |  |

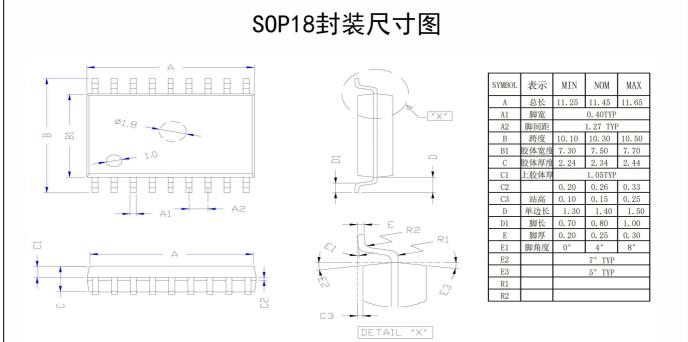

| XL9170               | XL9170  | S0P-18  | 11. 45*7. 5  | -20 to +75       | MSL3 | T&R       | 1000     |  |  |

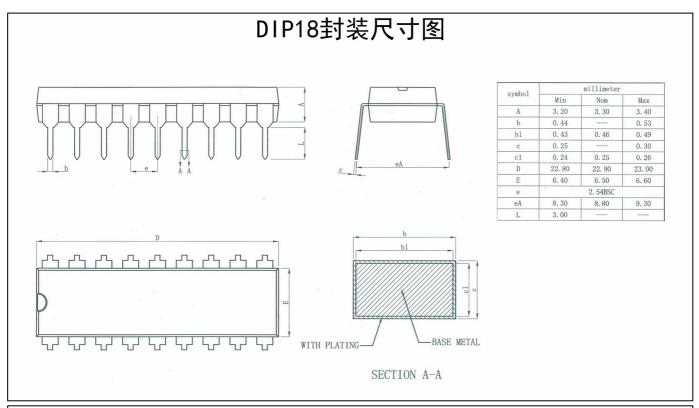

| XD9170               | XD9170  | DIP-18  | 22. 90*6. 50 | -20 to +75       | MSL3 | Tube 20   | 800      |  |  |

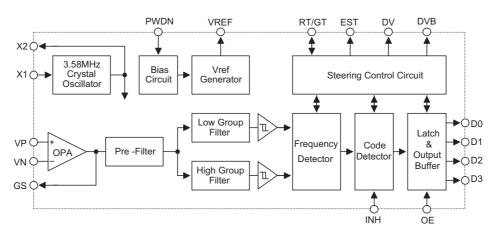

### **Block Diagram**

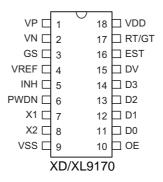

# **Pin Assignment**

# **Pin Description**

| Pin Name | I/O | Internal<br>Connection   | Description                                                                                                                            |

|----------|-----|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| VP       | I   | Operational<br>Amplifier | Operational amplifier non-inverting input                                                                                              |

| VN       | ı   |                          | Operational amplifier inverting input                                                                                                  |

| GS       | 0   |                          | Operational amplifier output terminal                                                                                                  |

| VREEF    | 0   | VREF                     | Reference voltage output, normally V <sub>DD</sub> /2                                                                                  |

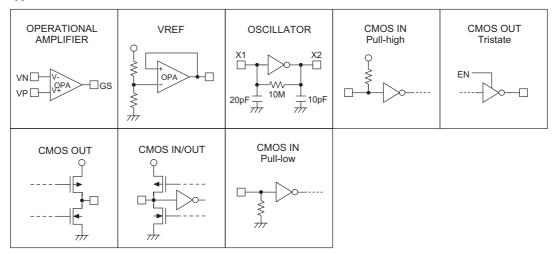

| X1       | ı   |                          | The system oscillator consists of an inverter, a bias resistor and the necessary                                                       |

| X2       | 0   | oscillator               | load capacitor on chip. A standard 3.579545MHz crystal connected to X1 and X2 terminals implements the oscillator function.            |

| PWDN     | I   | CMOS IN<br>Pull-low      | Active high. This enables the device to go into power down mode and inhibits the oscillator. This pin input is internally pulled down. |

| INH      | I   | CMOS IN<br>Pull-low      | Logic high. This inhibits the detection of tones representing characters A, B, C and D. This pin input is internally pulled down.      |

| VSS      | _   | _                        | Negative power supply, ground                                                                                                          |

| OE       | I   | CMOS IN<br>Pull-high     | D0~D3 output enable, high active                                                                                                       |

| D0~D3    | 0   | CMOS OUT<br>Tristate     | Receiving data output terminals OE="H": Output enable OE="L": High impedance                                                           |

| DV       | 0   | CMOS OUT                 | Data valid output When the chip receives a valid tone (DTMF) signal, the DV goes high; otherwise it remains low.                       |

| EST      | 0   | CMOS OUT                 | Early steering output (see Functional Description)                                                                                     |

| RT/GT    | I/O | CMOS IN/OUT              | Tone acquisition time and release time can be set through connection with external resistor and capacitor.                             |

| VDD      | _   | _                        | Positive power supply, 2.5V~5.5V for normal operation                                                                                  |

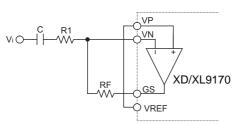

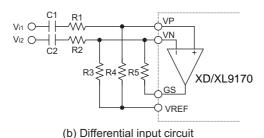

# Approximate internal connection circuits

# **Absolute Maximum Ratings**

| Supply Voltage0.3V to 6V                                    | Storage Temperature50°C to 125°C  |

|-------------------------------------------------------------|-----------------------------------|

| Input VoltageV <sub>SS</sub> -0.3V to V <sub>DD</sub> +0.3V | Operating Temperature20°C to 75°C |

Note: These are stress ratings only. Stresses exceeding the range specified under "Absolute Maximum Ratings" may cause substantial damage to the device. Functional operation of this device at other conditions beyond those listed in the specification is not implied and prolonged exposure to extreme conditions may affect device reliability.

# D.C. Characteristics Ta=25°C

| Symbol           | Parameter                       | •               | Test Conditions                      | Min.   | Trees  | Max.   | Unit |

|------------------|---------------------------------|-----------------|--------------------------------------|--------|--------|--------|------|

| Symbol           | Parameter                       | V <sub>DD</sub> | Conditions                           | IVIII. | Тур.   | wax.   |      |

| $V_{DD}$         | Operating Voltage               | _               | _                                    | 2.5    | 5      | 5.5    | V    |

| I <sub>DD</sub>  | Operating Current               | 5V              | _                                    | _      | 3.0    | 7      | mA   |

| I <sub>STB</sub> | Standby Current                 | 5V              | PWDN=5V                              | _      | 10     | 25     | μΑ   |

| V <sub>IL</sub>  | "Low" Input Voltage             | 5V              | _                                    | _      | _      | 1.0    | V    |

| V <sub>IH</sub>  | "High" Input Voltage            | 5V              | _                                    | 4.0    | _      | _      | V    |

| I <sub>IL</sub>  | "Low" Input Current             | 5V              | V <sub>VP</sub> =V <sub>VN</sub> =0V | _      | _      | 0.1    | μΑ   |

| I <sub>IH</sub>  | "High" Input Current            | 5V              | V <sub>VP</sub> =V <sub>VN</sub> =5V | _      | _      | 0.1    | μΑ   |

| R <sub>OE</sub>  | Pull-high Resistance (OE)       | 5V              | V <sub>OE</sub> =0V                  | 60     | 100    | 150    | kΩ   |

| R <sub>IN</sub>  | Input Impedance (VN, VP)        | 5V              | _                                    | _      | 10     | _      | MΩ   |

| I <sub>OH</sub>  | Source Current (D0~D3, EST, DV) | 5V              | V <sub>OUT</sub> =4.5V               | -0.4   | -0.8   | _      | mA   |

| I <sub>OL</sub>  | Sink Current (D0~D3, EST, DV)   | 5V              | V <sub>OUT</sub> =0.5V               | 1.0    | 2.5    | _      | mA   |

| fosc             | System Frequency                | 5V              | Crystal=3.5795MHz                    | 3.5759 | 3.5795 | 3.5831 | MHz  |

# A.C. Characteristics

f<sub>OSC</sub>=3.5795MHz, Ta=25°C

| Symbol           | Parameter                       |    | Test Conditions                          | Min.   | Tvo  | Max. | Unit            |

|------------------|---------------------------------|----|------------------------------------------|--------|------|------|-----------------|

| Symbol           | ol Parameter                    |    | Conditions                               | IVIII. | Тур. | wax. | Unit            |

| DTMF Sig         | gnal                            |    |                                          |        |      |      |                 |

|                  | Input Signal Level              |    |                                          | -36    | _    | -6   | dBm             |

|                  | Input Signal Level              | 5V |                                          | -29    | _    | 1    | uDIII           |

|                  | Twist Accept Limit (Positive)   | 5V |                                          | _      | 10   | _    | dB              |

|                  | Twist Accept Limit (Negative)   | 5V |                                          | _      | 10   | _    | dB              |

|                  | Dial Tone Tolerance             | 5V |                                          | _      | 18   | _    | dB              |

|                  | Noise Tolerance                 | 5V |                                          | _      | -12  | _    | dB              |

|                  | Third Tone Tolerance            | 5V |                                          | _      | -16  | _    | dB              |

|                  | Frequency Deviation Acceptance  | 5V |                                          | _      | _    | ±1.5 | %               |

|                  | Frequency Deviation Rejection   | 5V |                                          | ±3.5   | _    | _    | %               |

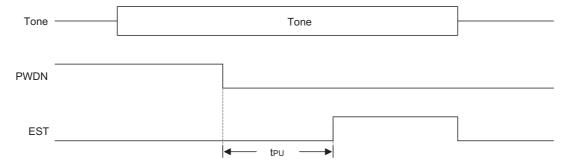

| t <sub>PU</sub>  | Power Up Time (See Figure 4.)   | 5V |                                          | _      | 30   | _    | ms              |

| Gain Sett        | ting Amplifier                  |    |                                          |        |      |      |                 |

| R <sub>IN</sub>  | Input Resistance                | 5V | _                                        | _      | 10   | _    | МΩ              |

| I <sub>IN</sub>  | Input Leakage Current           | 5V | $V_{SS}$ < $(V_{VP}, V_{VN})$ < $V_{DD}$ | _      | 0.1  | _    | μА              |

| Vos              | Offset Voltage                  | 5V | _                                        | _      | ±25  | _    | mV              |

| P <sub>SRR</sub> | Power Supply Rejection          | 5V |                                          | _      | 60   | _    | dB              |

| C <sub>MRR</sub> | Common Mode Rejection           | 5V | 100 Hz<br> -3V <v<sub>IN&lt;3V</v<sub>   | _      | 60   | _    | dB              |

| A <sub>VO</sub>  | Open Loop Gain                  | 5V | IIV -                                    | _      | 65   | _    | dB              |

| f <sub>T</sub>   | Gain Band Width                 | 5V | _                                        | _      | 1.5  | _    | MHz             |

| V <sub>OUT</sub> | Output Voltage Swing            | 5V | R <sub>L</sub> >100kΩ                    | _      | 4.5  | _    | V <sub>PP</sub> |

| R <sub>L</sub>   | Load Resistance (GS)            | 5V | _                                        | _      | 50   | _    | kΩ              |

| C <sub>L</sub>   | Load Capacitance (GS)           | 5V | _                                        | _      | 100  | _    | pF              |

| V <sub>CM</sub>  | Common Mode Range               | 5V | No load                                  | _      | 3.0  | _    | V <sub>PP</sub> |

| Steering         | Control                         |    |                                          |        |      |      |                 |

| t <sub>DP</sub>  | Tone Present Detection Time     |    |                                          | 5      | 16   | 22   | ms              |

| $t_{DA}$         | Tone Absent Detection Time      |    |                                          | _      | 4    | 8.5  | ms              |

| t <sub>ACC</sub> | Acceptable Tone Duration        |    |                                          | _      | _    | 42   | ms              |

| $t_{REJ}$        | Rejected Tone Duration          |    |                                          | 20     | _    | _    | ms              |

| t <sub>IA</sub>  | Acceptable Inter-digit Pause    |    |                                          |        |      | 42   | ms              |

| t <sub>IR</sub>  | Rejected Inter-digit Pause      |    |                                          | 20     | _    | _    | ms              |

| t <sub>PDO</sub> | Propagation Delay (RT/GT to DO) |    |                                          | _      | 8    | 11   | μS              |

| t <sub>PDV</sub> | Propagation Delay (RT/GT to DV) |    |                                          | _      | 12   | _    | μS              |

| t <sub>DOV</sub> | Output Data Set Up (DO to DV)   |    |                                          | _      | 4.5  | _    | μS              |

| t <sub>DDO</sub> | Disable Delay (OE to DO)        |    |                                          | _      | 300  | _    | ns              |

| t <sub>EDO</sub> | Enable Delay (OE to DO)         |    |                                          | _      | 50   | 60   | ns              |

Note: DO=D0~D3

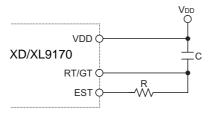

Figure 1. Test circuit

### **Functional Description**

#### Overview

TheXD/XL9170 tone decoders consist of three band pass filters and two digital decode circuits to convert a tone (DTMF) signal into digital code output.

An operational amplifier is built-in to adjust the input signal (refer to Figure 2).

(a) Standard input circuit

Figure 2. Input operation for amplifier application circuits

The pre-filter is a band rejection filter which reduces the dialing tone from 350Hz to 400Hz.

The low group filter filters low group frequency signal output whereas the high group filter filters high group frequency signal output.

Each filter output is followed by a zero-crossing detector with hysteresis. When each signal amplitude at the output exceeds the specified level, it is transferred to full swing logic signal.

When input signals are recognized to be effective, DV becomes high, and the correct tone code (DTMF) digit is transferred

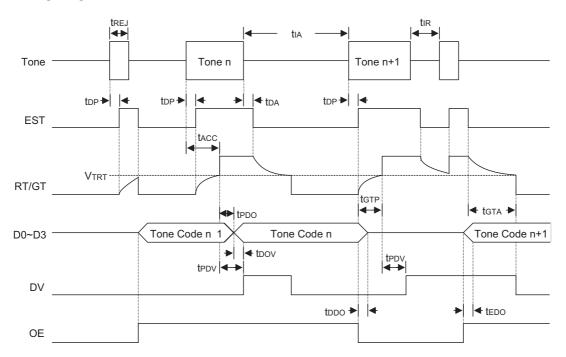

#### Steering control circuit

The steering control circuit is used for measuring the effective signal duration and for protecting against drop out of valid signals. It employs the analog delay by external RC time-constant controlled by EST.

The timing is shown in Figure 3. The EST pin is normally low and draws the RT/GT pin to keep low through discharge of external RC. When a valid tone input is detected, EST goes high to charge RT/GT through RC.

When the voltage of RT/GT changes from 0 to V<sub>TRT</sub> (2.35V for 5V supply), the input signal is effective, and the correct code will be created by the code detector. After D0~D3 are completely latched, DV output becomes high. When the voltage of RT/GT falls down from VDD to V<sub>TRT</sub> (i.e.., when there is no input tone), DV output becomes low, and D0~D3 keeps data until a next valid tone input is produced.

By selecting adequate external RC value, the minimum acceptable input tone duration ( $t_{ACC}$ ) and the minimum acceptable inter-tone rejection ( $t_{IR}$ ) can be set. External components (R, C) are chosen by the formula (refer to Figure 5.):

$t_{ACC} = t_{DP} + t_{GTP};$

t<sub>IR</sub>=t<sub>DA</sub>+t<sub>GTA</sub>;

where  $\ t_{ACC}$ : Tone duration acceptable time

t<sub>DP</sub>: EST output delay time ("L"→"H")

t<sub>GTP</sub>: Tone present time

$t_{IR}$ : Inter-digit pause rejection time  $t_{DA}$ : EST output delay time ("H" $\rightarrow$ "L")

t<sub>GTA</sub>: Tone absent time

# **Timing Diagrams**

Figure 3. Steering timing

Figure 4. Power up timing

# (a) Fundamental circuit:

$$\begin{split} t_{GTP} &= R \times C \times Ln \; (V_{DD} \, / \, (V_{DD} \, - \, V_{TRT})) \\ t_{GTA} &= R \times C \times Ln \; (V_{DD} \, / \, V_{TRT}) \end{split}$$

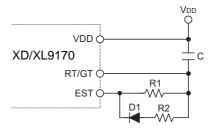

# (c) $t_{GTP} > t_{GTA}$ :

$$t_{GTP} = R1 \times C \times Ln (V_{DD} / (V_{DD} - V_{TRT}))$$

$t_{GTA} = (R1 // R2) \times C \times Ln (V_{DD} / V_{TRT})$

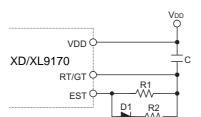

$$\begin{split} t_{\text{GTP}} &= (\text{R1 // R2}) \times \text{C} \times \text{Ln (V}_{\text{DD}} - \text{V}_{\text{TRT}})) \\ t_{\text{GTA}} &= \text{R1} \times \text{C} \times \text{Ln (V}_{\text{DD}} / \text{V}_{\text{TRT}}) \end{split}$$

Figure 5. Steering time adjustment circuits

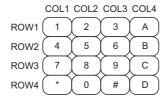

# **DTMF** dialing matrix

# DTMF data output table

| Low Group (Hz) | High Group (Hz) | Digit | OE | D3 | D2 | D1 | D0 |

|----------------|-----------------|-------|----|----|----|----|----|

| 697            | 1209            | 1     | Н  | L  | L  | L  | Н  |

| 697            | 1336            | 2     | Н  | L  | L  | Н  | L  |

| 697            | 1477            | 3     | Н  | L  | L  | Н  | Н  |

| 770            | 1209            | 4     | Н  | L  | Н  | L  | L  |

| 770            | 1336            | 5     | Н  | L  | Н  | L  | Н  |

| 770            | 1477            | 6     | Н  | L  | Н  | Н  | L  |

| 852            | 1209            | 7     | Н  | L  | Н  | Н  | Н  |

| 852            | 1336            | 8     | Н  | Н  | L  | L  | L  |

| 852            | 1477            | 9     | Н  | Н  | L  | L  | Н  |

| 941            | 1336            | 0     | Н  | Н  | L  | Н  | L  |

| 941            | 1209            | *     | Н  | Н  | L  | Н  | Н  |

| 941            | 1477            | #     | Н  | Н  | Н  | L  | L  |

| 697            | 1633            | Α     | Н  | Н  | Н  | L  | Н  |

| 770            | 1633            | В     | Н  | Н  | Н  | Н  | L  |

| 852            | 1633            | С     | Н  | Н  | Н  | Н  | Н  |

| 941            | 1633            | D     | Н  | L  | L  | L  | L  |

| _              | _               | ANY   | L  | Z  | Z  | Z  | Z  |

Note: "Z" High impedance; "ANY" Any digit

### Data output

The data outputs (D0~D3) are tristate outputs. When OE input becomes low, the data outputs (D0~D3) are high impedance.

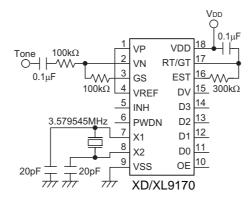

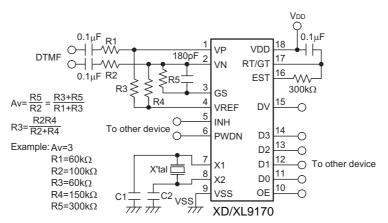

# **Application Circuits**

# **Application Circuit 1**

Note: X'tal = 3.579545MHz crystal

C1 = C2 ≅ 20pF

X'tal = 3.58MHz ceramic resonator

$C1 = C2 \cong 39pF$

### **Application Circuit 2**

Note: X'tal = 3.579545MHz crystal

$C1 = C2 \cong 20pF$

X'tal = 3.58MHz ceramic resonator

C1 = C2 ≅ 39pF

Xinluda reserves the right to change the above information without prior notice.