### SX1243 - Low Cost Low Current Integrated Transmitter

### 310 to 928MHz Frequency Agile

### **GENERAL DESCRIPTION**

The SX1243 is an ultra-low-cost, fully integrated FSK or OOK transmitter suitable for operation between 310 and 450 MHz, 860 and 870 MHz, as well as 902 and 928 MHz.

For applications where economy is paramount, the SX1243 may be used without the requirement for configuration via an MCU. However, in conjunction with a microcontroller the communication link parameters may be re-configured. Including, output power, modulation format and operating channel.

The SX1243 offers integrated radio performance with cost efficiency and is suited for operation in North America FCC Part 15.231, FCC Part 15.247 FHSS and Digital Modulation Techniques, 15.249, and Europe EN 300 220.

### **ORDERING INFORMATION**

| Part Number  | Temperature Range | Package | MOQ / Multiple |

|--------------|-------------------|---------|----------------|

| SX1243IULTRT | -40 °C to +85 °C  | DFN-UT8 | 3000 pieces    |

Pb-Free, Halogen Free, RoHS/WEEE compliant product.

### APPLICATIONS

- Garage Door Openers

- Low-Cost Consumer Electronic Applications

- Remote Keyless Entry (RKE)

- Remote Control / Security Systems

### **KEY PRODUCT FEATURES**

- +10 dBm or 0 dBm Configurable output power

- Bit rates up to 100 kbps

- OOK and FSK modulation.

- 1.8 to 3.7 V supply range.

- Low BOM Fully Integrated Tx

- Fractional-N PLL with 1.5 kHz typical step

- Frequency agility for FHSS modulation

- FCC CFR Part 15.247 Digital Modulation Techniques

## DATASHEET

### **Table of contents**

#### Section

| 1. | Circuit Description                        | . 3 |

|----|--------------------------------------------|-----|

|    | 1.1. General Description                   | . 3 |

|    | 1.2. Block Diagram                         | . 3 |

|    | 1.3. Marking Diagram                       | . 4 |

|    | 1.4. Pin Description, DFN8 Encapsulation   | 5   |

| 2. | Electrical Characteristics                 |     |

|    | 2.1. ESD Notice                            | . 6 |

|    | 2.2. Absolute Maximum Ratings              | . 6 |

|    | 2.3. Operating Range                       |     |

|    | 2.4. Electrical Specifications             |     |

| 3. | Digital Specification                      |     |

| 4. | Application Modes of the SX1243            |     |

|    | 4.1. Transmitter Modes                     |     |

|    | 4.2. Mode Selection Flowchart              |     |

|    | 4.3. Application Mode: Power & Go          |     |

|    | 4.4. Application Mode: Advanced            |     |

|    | 4.4.1. Advanced Mode: Configuration        |     |

|    | 4.4.2. Frequency Hopping Spread Spectrum   |     |

|    | 4.5. Frequency Band Coverage               |     |

|    | 4.6. Power Consumption                     |     |

| 5. | SX1243 Configuration                       |     |

| 0. | 5.1. TWI Access                            |     |

|    | 5.2. APPLICATION Configuration Parameters  |     |

|    | 5.3. FREQUENCY Configuration Parameters    |     |

|    | 5.4. Test Parameters                       |     |

|    | 5.5. Status Parameters                     |     |

|    | 5.6. Recovery Command                      |     |

| 6. | Application Information                    |     |

| 0. | 6.1. Crystal Specification                 |     |

|    | 6.2. Evaluation Module                     |     |

|    | 6.3. NRESET Pin                            |     |

|    | 6.4. TX_READY Pin                          |     |

|    | 6.5. Low Power Optimization                |     |

|    | 6.5.1. 2 Connections: CTRL, DATA           |     |

|    | 6.5.2. 3 Connections: CTRL, DATA, TX_READY |     |

| 7. | SX1243 Packaging                           |     |

|    | 7.1. Package Outline Drawing               |     |

|    | 7.2. Thermal Impedance                     |     |

|    | 7.3. Land Pattern                          |     |

|    | 7.4. Tape & Reel Specification             |     |

| 8. | Revision History                           |     |

| 0. |                                            | 20  |

# SX1243

## DATASHEET

Page

This product datasheet contains a detailed description of the SX1243 performance and functionality.

### 1. Circuit Description

#### 1.1. General Description

The SX1243 is a fully-integrated multi-band, single chip transmitter IC capable of FSK and OOK modulation of an input data stream.

It contains a frequency synthesizer which is a fractional-N sigma-delta PLL. For frequency modulation (FSK), the modulation is made inside the PLL bandwidth. For amplitude modulation (OOK), the modulation is performed by turning on and off the output PA.

The frequency reference used by the PLL is generated by a 22, 24 or 26 MHz crystal oscillator, depending on the frequency band of interest.

The Power Amplifier (PA), connected to the RFOUT pin, can deliver 0 dBm or +10 dBm in a 50  $\Omega$  load. Each of these two output powers need a specific matching network when efficiency needs to be optimized.

The circuit can be configured via a simplified TWI interface, constituted of pin CTRL and DATA. The pins of this interface are also used to transmit the modulating data to the chip.

Another key feature of the SX1243 is its low current consumption in Transmit and Sleep modes and its wide voltage operating range from 1.8 V to 3.7 V. This makes the SX1243 suitable for low-cost battery chemistries or energy harvesting applications.

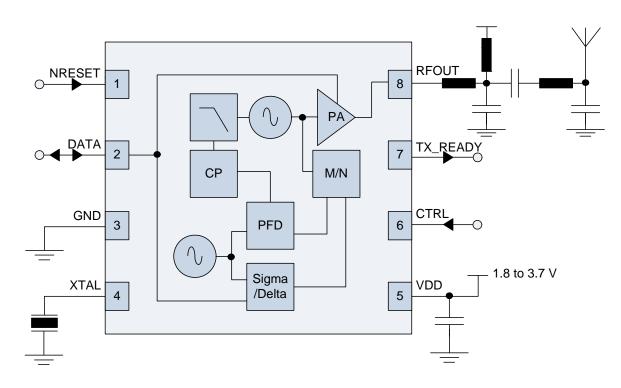

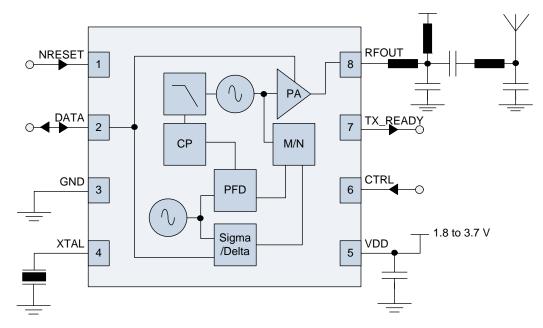

#### 1.2. Block Diagram

The figure below shows the simplified block diagram of the SX1243 die mounted in a DFN8 package.

Figure 1. SX1243 Simplified Block Diagram and BOM

## SX1243 Integrated Transmitter IC

### DATASHEET

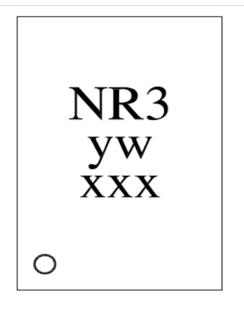

#### 1.3. Marking Diagram

Figure 2. Marking Diagram

- nnn = Relates to the part number

- yw = Date code

- xxx = Lot No

### 1.4. Pin Description, DFN8 Encapsulation

Table 1

Description of the SX1243 DFN8 Pinouts

| Number | Name     | Туре | Function in 'Power & Go' Modes | Function in 'Advanced' Mode    |  |  |  |  |  |  |

|--------|----------|------|--------------------------------|--------------------------------|--|--|--|--|--|--|

| 0      | GND      | I    | Exposed Pad, Ground            |                                |  |  |  |  |  |  |

| 1      | NRESET   | I    | Reset (Optional, ca            | an be left floating)           |  |  |  |  |  |  |

| 2      | DATA     | I/O  | Transmit Data                  | Transmit or Configuration Data |  |  |  |  |  |  |

| 3      | GND      | I    | Ground                         |                                |  |  |  |  |  |  |

| 4      | XTAL     | I/O  | Reference                      | e Crystal                      |  |  |  |  |  |  |

| 5      | VBAT     | I    | Power Supply                   | 1.8V to 3.7V                   |  |  |  |  |  |  |

| 6      | CTRL     | I    | Config Selection               | Configuration Data Clock       |  |  |  |  |  |  |

| 7      | TX_READY | 0    | Transmitter Ready Flag (Op     | otional, can be left floating) |  |  |  |  |  |  |

| 8      | RFOUT    | 0    | Transmitter                    | RF Output                      |  |  |  |  |  |  |

### 2. Electrical Characteristics

#### 2.1. ESD Notice

The SX1243 is an electrostatic discharge sensitive device. It satisfies Class 2 of the JEDEC standard JESD22-A114-B (Human Body Model) on all pins.

#### 2.2. Absolute Maximum Ratings

Stresses above the values listed below may cause permanent device failure. Exposure to absolute maximum ratings for extended periods may affect device reliability.

#### Table 2 Absolute Maximum Ratings

| Symbol | Description          | Min  | Max | Unit |

|--------|----------------------|------|-----|------|

| VDDmr  | Supply Voltage       | -0.5 | 3.9 | V    |

| Tmr    | Temperature          | -55  | 115 | °C   |

| Tjunc  | Junction Temperature | -55  | 125 | ° C  |

| Tstor  | Storage Temperature  | -55  | 150 | °C   |

#### 2.3. Operating Range

Operating ranges define the limits for functional operation and the parametric characteristics of the device as described in this section. Functionality outside these limits is not implied.

#### Table 3Operating Range

| Symbol | Description                       | Min | Max | Unit |

|--------|-----------------------------------|-----|-----|------|

| VDDop  | Supply voltage                    | 1.8 | 3.7 | V    |

| Тор    | Operational temperature range     | -40 | 85  | °C   |

| Clop   | Load capacitance on digital ports | -   | 25  | pF   |

#### 2.4. Electrical Specifications

WIRELESS & SENSING

The table below gives the electrical specifications of the transmitter under the following conditions: Supply voltage VBAT = 3.3 V, temperature = 25 °C,  $f_{XOSC}$  = 26 MHz,  $f_{RF}$  = 915 MHz, 2-FSK modulation with Fdev=+/-10 kHz, bit rate = 10 kbit/s and output power = +10 dBm terminated in a matched 50 Ohm impedance, unless otherwise specified.

#### Table 4Transmitter Specifications

| Symbol     | Description                                            | Conditions                                              | Min         | Тур                       | Мах         | Unit                                 |

|------------|--------------------------------------------------------|---------------------------------------------------------|-------------|---------------------------|-------------|--------------------------------------|

| Current Co | nsumption                                              |                                                         |             |                           |             |                                      |

| IDDSL      | Supply current in Sleep mode                           |                                                         | -           | 125                       |             | nA                                   |

| IDDT_315   | Supply current in Transmit mode<br>at 315 MHz*         | RFOP=+10dBm 50% OOK<br>RFOP=+10dBm FSK<br>RFOP=0dBm FSK | -<br>-<br>- | 11<br>15<br>9             |             | mA<br>mA<br>mA                       |

| IDDT_915   | Supply current in Transmit mode at 915 MHz*            | RFOP=+10dBm FSK<br>RFOP=0dBm FSK                        | -           | 17.5<br>10.5              | -           | mA<br>mA                             |

| RF and Bas | seband Specifications                                  |                                                         |             |                           |             |                                      |

| FBAND      | Accessible Frequency Bands                             | Band 0, with FXOSC=22 MHz                               | 310         | -                         | 450         | MHz                                  |

|            | See details in Table 7.                                | Band 0, with FXOSC=24 MHz                               | 312         | -                         | 450         | MHz                                  |

|            |                                                        | Band 0, with FXOSC=26 MHz                               | 338         | -                         | 450         | MHz                                  |

|            |                                                        | Band 1, with FXOSC=26 MHz                               | 860<br>902  | -                         | 870<br>928  | MHz<br>MHz                           |

| FDA        | Frequency deviation, FSK                               |                                                         | 10          | -                         | 200         | kHz                                  |

| BRF        | Bit rate, FSK                                          | Permissible Range                                       | 0.5         | -                         | 100         | kbps                                 |

| BRO        | Bit rate, OOK                                          | Permissible Range                                       | 0.5         | -                         | 10          | kbps                                 |

| OOK_B      | OOK Modulation Depth                                   |                                                         | -           | 45                        | -           | dB                                   |

| RFOP       | RF output power in 50 Ohms<br>in either frequency band | High Power Setting<br>Low Power Setting*                | 7<br>-3     | 10<br>0                   | -           | dBm<br>dBm                           |

| RFOPFL     | RF output power flatness                               | From 315 to 390 MHz, 50 Ohms load                       | -           | 2                         | -           | dB                                   |

| DRFOPV     | Variation in RF output power with supply voltage       | 2.5 V to 3.3 V<br>1.8 V to 3.7 V                        | -           | -                         | 3<br>7      | dB<br>dB                             |

| PHN        | Transmitter phase noise                                | At offset: 100 kHz<br>350 kHz<br>550 kHz<br>1.15 MHz    |             | -84<br>-94<br>-96<br>-105 | -<br>-<br>- | dBc/Hz<br>dBc/Hz<br>dBc/Hz<br>dBc/Hz |

| STEP_22    | RF frequency step                                      | FXOSC = 22 MHz, Band 0                                  | -           | 1.34277                   | -           | kHz                                  |

| STEP_24    | RF frequency step                                      | FXOSC = 24 MHz, Band 0                                  | -           | 1.46484                   | -           | kHz                                  |

| STEP_26    | RF frequency step                                      | FXOSC = 26 MHz, Band 0<br>FXOSC = 26 MHz, Band 1        | -           | 1.58691<br>3.17383        | -           | kHz<br>kHz                           |

## SX1243 Integrated Transmitter IC

### DATASHEET

| Symbol     | Description                          | Conditions                                | Min         | Тур                | Max         | Unit              |

|------------|--------------------------------------|-------------------------------------------|-------------|--------------------|-------------|-------------------|

| FXOSC      | Crystal Oscillator Frequency         |                                           | -<br>-<br>- | 22<br>24<br>26     | -<br>-<br>- | MHz<br>MHz<br>MHz |

| DFXOSC     | Frequency Variation of the XOSC      | No crystal contribution                   | -           | -                  | +/-25       | ppm               |

| Timing Spe | cifications                          |                                           |             |                    |             |                   |

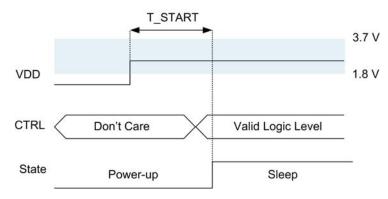

| TS_TR      | Time from Sleep to Tx mode           | XTAL dependant, with spec'd XTAL          | -           | 650                | 2000        | us                |

| TS_HOP0    | Channel hop time in Band 0           | 315 to 390 MHz                            | -           | 250                | 500         | us                |

| TS_HOP1    | Channel hop time in Band 1           | Maximum hop of 26 MHz***                  | -           | 200                | 400         | us                |

| TOFFT      | Timer from Tx data activity to Sleep | Programmable                              | -           | 2<br>20            | -           | ms<br>ms          |

| RAMP       | PA Ramp up and down time             |                                           | -           | 20                 | -           | us                |

| T_START    | Time before CTRL pin mode selection. | Time from power on to sampling of CTRL ** | -           | 200 us<br>+ TS_OSC | -           | ms                |

\* With different matching networks

\*\* The oscillator startup time, TS\_OSC, depends on the electrical characteristics of the crystal

\*\*\* From the last CTRL falling edge of the Frequency change instruction to transmitter ready (PA ramp up finished)

### 3. Digital Specification

The following table gives the operating specifications for the digital inputs and outputs of the SX1243.

#### Table 5 Digital Signals Specification

| Symbol                          | Description                                    | Conditions                               | Min | Тур | Max | Unit |

|---------------------------------|------------------------------------------------|------------------------------------------|-----|-----|-----|------|

| V <sub>IH</sub>                 | Digital input level high                       |                                          | 0.8 | -   | -   | VBAT |

| V <sub>IL</sub>                 | Digital input level low                        |                                          | -   | -   | 0.2 | VBAT |

| V <sub>OH</sub>                 | Digital output level high                      | Imax = 1 mA                              | 0.9 | -   | -   | VBAT |

| V <sub>OL</sub>                 | Digital output level low                       | Imax = -1 mA                             | -   | -   | 0.1 | VBAT |

| f <sub>CTRL</sub>               | CTRL Clock Frequency                           |                                          | -   | -   | 10  | MHz  |

| t <sub>ch</sub>                 | CTRL Clock High time                           |                                          | 45  | -   | -   | ns   |

| t <sub>cl</sub>                 | CTRL Clock Low time                            |                                          | 45  | -   | -   | ns   |

| t <sub>rise</sub>               | CTRL Clock rise time                           |                                          | -   | -   | 5   | ns   |

| t <sub>fall</sub>               | CTRL Clock Fall time                           |                                          | -   | -   | 5   | ns   |

| t <sub>setup</sub>              | DATA Setup time                                | From Data transition to CTRL rising edge | 45  | -   | -   | ns   |

| t <sub>hold</sub>               | DATA hold time                                 | From CTRL rising edge to DATA transition | 45  | -   | -   | ns   |

| t <sub>0</sub> , t <sub>2</sub> | Time at "1" on DATA during<br>Recovery command | See Figure 10 and Figure 11              | -   | -   | 5   | us   |

| t <sub>1</sub>                  | Time at "0" on DATA during<br>Recovery command | See Figure 11                            | 5   | -   | -   | us   |

### 4. Application Modes of the SX1243

Pins CTRL and DATA are used for both configuring the circuit and sending the data to be transmitted over the air. Two different modes are associated to these pins, "**Power&Go**" and "**Advanced**" modes.

#### 4.1. Transmitter Modes

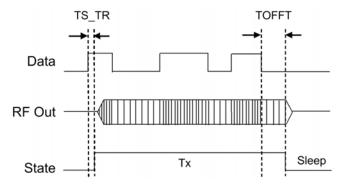

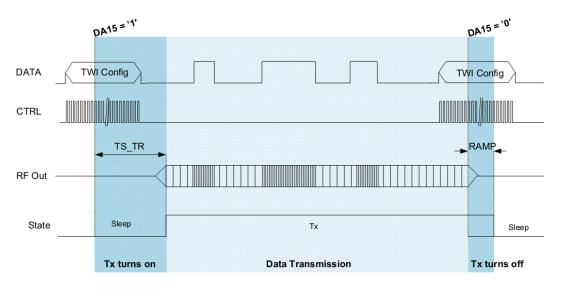

Automatic Mode operation is described in Figure 3. Here we see that a rising edge on the DATA pin activates the transmitter start-up process. DATA must be held high for the start-up time (TS\_TR) of the SX1243. During this time the SX1243 undergoes an optimized, self-calibrating trajectory from Sleep mode to Transmit mode. Once this time has elapsed, the SX1243 is ready to transmit. Any logical signal subsequently applied to the DATA pin is then transmitted.

Figure 3. 'Power & Go' Mode: Transmitter Timing Operation

The transition back to Sleep mode is managed automatically. The SX1243 waits for TOFFT (2 or 20 ms) of inactivity on DATA before returning to Sleep mode.

In **Forced Transmit Mode** the circuit can be forced to wake up and go to TX mode by sending an APPLICATION instruction through the TWI interface, and setting the Mode bit DA(15) to '1'. Once in Transmit the circuit will transmit over the air the data stream presented on the DATA pin. The circuit will stay in transmit mode until a new APPLICATION instruction is sent with DA(15) to '0'.

DATASHEET

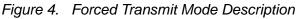

#### 4.2. Mode Selection Flowchart

Figure 5. SX1243 Mode Selection

Note: Advanced mode is entered only if DATA is held low during CTRL's rising edge.

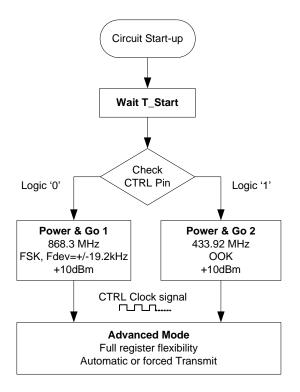

When powering up the circuit (microcontroller and SX1243), the logic level of the CTRL pin is sampled after T\_START, as described on Figure 6. During T\_START, the microcontroller IO driving the CTRL pin must be configured as an output, driving the CTRL pin to the desired state.

Figure 6. Power-up Timing

#### 4.3. Application Mode: Power & Go

The default 'Power & Go' application mode sees the SX1243 configured as detailed in Table 6. By changing the logical state of the CTRL pin at Power-up or Reset, two distinct configuration modes can be selected. The Power & Go application modes hence permit microcontroller-less operation.

#### Table 6 Configuration in Power & Go Mode

| CTRL Pin | Configuration                            | Mode       |

|----------|------------------------------------------|------------|

| 'Low'    | FSK 868.3 MHz, +10 dBm, Fdev=+/-19.2 kHz | Power&Go 1 |

| 'High'   | OOK 433.92 MHz, +10 dBm                  | Power&Go 2 |

#### 4.4. Application Mode: Advanced

#### 4.4.1. Advanced Mode: Configuration

As described on Figure 5, Advanced mode is entered when accessing the Two Wire Interface (TWI) bus of the SX1243. Upon communication to the register at up to 10 MHz of clocking speed, complete flexibility on the use of the chip is obtained.

Once all register settings are selected (see registers detailed description in section [5]), the SX1243 can be used either in Automatic mode by simply toggling the DATA pin, or in Forced Transmit mode to optimize timings for instance.

#### 4.4.2. Frequency Hopping Spread Spectrum

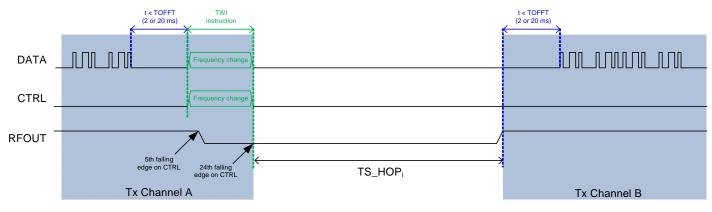

**Frequency hopping** is supported in Advanced mode. After sending the data stream in the first channel, the user can send a Frequency change instruction containing the new channel frequency. The circuit will automatically ramp down the PA, lock the PLL to the new frequency, and turn the Power Amplifier back on. The user can then send his packet data on the new channel. Timings are detailed hereafter:

Figure 7. Frequency Hopping Description

Notes: - During any TWI access, the input of the modulator is inhibited

- The time between two Frequency change instructions shall be greater than TS\_HOPi

- FHSS modulation, as described under FCC part 15.247, is supported by the SX1243; also note that the large Frequency Deviation settings available on the SX1243 make it suitable for "Digitally Modulated Systems", as described under FCC Part 15.247 (a)(2)

#### 4.5. Frequency Band Coverage

The SX1243 offers several combinations or frequency references and frequency outputs, allowing for maximum flexibility and design of multi-band products:

#### Table 7 Frequency Selection Table

| Reference<br>Frequency<br>FXOSC | Band Setting<br>DA(13) | Upper / Lower<br>Frequency<br>Bounds    | Fstep                                          | Frf &<br>Fdev                               |

|---------------------------------|------------------------|-----------------------------------------|------------------------------------------------|---------------------------------------------|

| 22 MHz                          |                        | 310 to 450 MHz                          | $Fstep = \frac{22x10^6}{2^{14}} = 1.34277kHz$  |                                             |

| 24 MHz                          | 0                      | 312 to 450 MHz                          | $Fstep = \frac{24x10^6}{2^{14}} = 1.46484kHz$  | Frf= DF(18;0)×Fstep<br>Fdev= DA(12;5)×Fstep |

| 26 MHz                          |                        | 338 to 450 MHz                          | $Fstep = \frac{26x10^6}{2^{14}} = 1.58691 kHz$ |                                             |

|                                 | 1                      | 860 to 870 MHz<br>and<br>902 to 928 MHz | $Fstep = \frac{26x10^6}{2^{13}} = 3.17383kHz$  |                                             |

#### 4.6. Power Consumption

The following typical power consumption figures are observed on the SX1243 kits. Note that the transmitter efficiency depends on the impedance matching quality, and can be PCB design dependant.

The PA matching may be different in each frequency band.

#### Table 8 Power Consumption in Tx mode

| Frequency Band | Conditions                                                                                                  | Typical Current<br>Drain |

|----------------|-------------------------------------------------------------------------------------------------------------|--------------------------|

| 310 to 450 MHz | Pout=+10dBm, OOK modulation with 50% duty cycle<br>Pout=+10dBm, FSK modulation<br>Pout=0dBm, FSK modulation | 11 mA<br>15 mA<br>9 mA   |

| 860 to 870 MHz | Pout=+10dBm, FSK modulation<br>Pout=0dBm, FSK modulation                                                    | 16.5 mA<br>10 mA         |

| 902 to 928 MHz | Pout=+10dBm, FSK modulation<br>Pout=0dBm, FSK modulation                                                    | 17.5 mA<br>10.5 mA       |

### 5. SX1243 Configuration

The SX1243 has several configuration parameters which can be selected through the serial interface.

#### 5.1. TWI Access

As long as CTRL is kept stable, the DATA pin is considered by the circuit as the input for the data to be transmitted over the air (Power&Go modes).

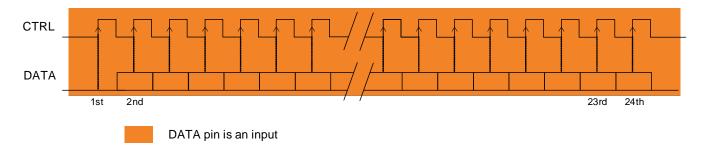

Programming of the configuration register is triggered by a rising edge on the CTRL line. Upon detection of this rising edge, the data applied to the DATA pin is accepted as register configuration information, the data bits are clocked on subsequent rising edges of the clocking signal applied to the CTRL pin. The timing for SX1243 configuration register 'write' is shown in Figure 8. Note that, once triggered, all 24 clock cycle must be issued to the SX1243.

Figure 8. TWI Configuration Register 'Write'.

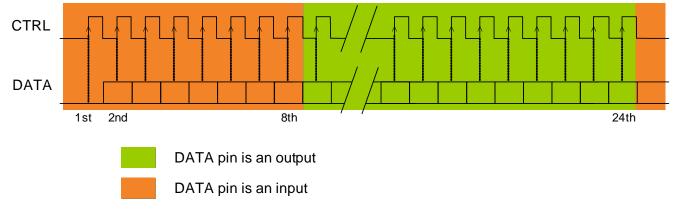

The registers may, similarly, be read using the timing of Figure 9.

Figure 9. TWI Configuration Register 'Read'.

The first rising edge on CTRL which initiates the ADVANCED mode must occur at least 1 ms after the circuit has been powered up or reset.

DATASHEET

#### Table 9TWI Instruction Table

|   | Byte 0 |   |   |   |      |      |                      |                               | B   | yte  | 1    |     |          |      |     | E   | 3yt | e 2 | 2 |                |           | Instruction |                                                                        |

|---|--------|---|---|---|------|------|----------------------|-------------------------------|-----|------|------|-----|----------|------|-----|-----|-----|-----|---|----------------|-----------|-------------|------------------------------------------------------------------------|

| 7 | 6      | 5 | 4 | 3 | 2    | 1    | 0                    | 7                             | 6 5 | 5 4  | 3    | 2   | 2 1      | 0    | 7   | 6   | 5   | 4   | 3 | 2              | 1         | 0           |                                                                        |

| 0 | 0      | 0 | 0 |   | 000  | )0)  |                      |                               |     |      |      |     | D        | DA(1 | 5:0 | ))  |     |     |   |                |           |             | Write Application bits                                                 |

| 0 | 0      | 0 | 1 | 1 |      |      |                      |                               |     |      |      | D   | F(18     | 3:0) |     |     |     |     |   |                |           |             | Write Frequency bits                                                   |

| 0 | 0      | 1 | 0 |   | (    | 0)(( | )0 <sup>-</sup>      | 10)(                          | 001 | 0)   |      |     |          |      |     | DT( | 10: | :0) |   |                |           |             | Write Test bits (pad protected)                                        |

| 0 | 0      | 1 | 1 |   | (00  | 11)  |                      |                               |     |      |      |     | C        | DA(1 | 5:0 | ))  |     |     |   |                |           |             | Read Application bits                                                  |

| 0 | 1      | 0 | 0 |   | 010  | 00)  |                      |                               |     |      |      |     | C        | )F(1 | 5:0 | ))  |     |     |   |                |           |             | Read the 16 least significant Frequency bits                           |

| 0 | 1      | 0 | 1 |   | 010  | )1)  |                      |                               |     | DS   | (12: | :5) |          |      |     | DS  | (4: | 0)  |   | DI<br>16       | =(1<br>S) | 8:          | <b>Read</b> Chip version, Status and 3 most significant Frequency bits |

| 0 | 1      | 1 | 0 |   | (011 | 10)  |                      |                               |     |      |      |     | D        | S(28 | 8:1 | 3)  |     |     |   |                |           |             | Read Bist signature                                                    |

| 0 | 1      | 1 | 1 |   | (01  | 11)  |                      | (                             | 111 | 1)(1 | )    |     | DT(10:0) |      |     |     |     |     |   | Read Test bits |           |             |                                                                        |

| 1 | 1 x    |   |   |   |      |      |                      | Discarded, not an instruction |     |      |      |     |          |      |     |     |     |     |   |                |           |             |                                                                        |

|   | All 1  |   |   |   |      |      | Recovery instruction |                               |     |      |      |     |          |      |     |     |     |     |   |                |           |             |                                                                        |

Notes - The first "0" transmitted to the SX1243 is required to initialize communication

- The following 3 bits (highlighted in blue) determine the type of instruction

- The forthcoming bits (highlighted in green) define a protection pattern; any error in these bits voids the instruction

### 5.2. APPLICATION Configuration Parameters

| Name  | Number   | Description                                                                                                                                         | Power<br>&Go 1              | Power<br>&Go 2 |

|-------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|----------------|

| Mode  | DA(15)   | Mode:<br>0 → Automatic mode<br>1 → Forced transmit mode                                                                                             |                             | 0              |

| Modul | DA(14)   | Modulation scheme:<br>0 → FSK<br>1 → OOK                                                                                                            | 0                           | 1              |

| Band  | DA(13)   | Band 0, 310 to 450 MHz<br>Band 1, 860 to 870 MHz and 902 to 928 MHz                                                                                 | 1                           | 0              |

| Fdev  | DA(12:5) | RF Frequency deviation in FSK mode only<br>See Table 7 for details                                                                                  | 0x06<br>Fdev=<br>+/-19.2kHz | Unused         |

| Pout  | DA(4)    | Output power range:<br>0 → 0 dBm<br>1 → 10 dBm                                                                                                      | 1                           | 1              |

| TOFFT | DA(3)    | Period of inactivity on DATA before SX1243<br>enters Sleep mode in Automatic mode:<br>$0 \rightarrow 2 \text{ ms}$<br>$1 \rightarrow 20 \text{ ms}$ | 0                           | 1              |

| RES   | DA(2:0)  | Reserved                                                                                                                                            | 100                         | 100            |

Table 10 APPLICATION Configuration Parameters

Note: All changes to the APPLICATION parameters must be performed when the device is in Sleep mode, with the exception of DA(15). Mode can be sequentially written to "1", and then "0" while the device is in Transmit mode, to speed up the turn off process and circumvent the TOFFT delay.

#### 5.3. FREQUENCY Configuration Parameters

| Na  | me | Number   | Description             | Power<br>&Go 1                            | Power<br>&Go 2                             |

|-----|----|----------|-------------------------|-------------------------------------------|--------------------------------------------|

| Frf |    | DF(18:0) | RF operating frequency  | 0x42CAD                                   | 0x42C1C                                    |

|     |    |          | See Table 7 for details | Frf=868.3 MHz<br>With 26 MHz<br>reference | Frf=433.92 MHz<br>With 26 MHz<br>reference |

#### Table 11 FREQUENCY Configuration Parameters

If done in Sleep mode, the Frequency change instruction will be applied next time the SX1243 is turned on. If Frequency change occurs during transmission, the automated Frequency Hopping sequence described in section [4.4.2] will take place.

#### 5.4. Test Parameters

Ten Test bits DT(9:0) exist in the SX1243. They are only use for the industrial test of the device, and therefore they are pad protected. It means that their value cannot be modified without applying a specific logical level to some of the SX1243 pads during a write access.

#### 5.5. Status Parameters

DS(12:5) are read-only bits, organized as follows:

| Name            | Number    | Description                                                                                                    | Default<br>Advanced<br>Mode | Power<br>&Go 1 | Power<br>&Go 2 |  |

|-----------------|-----------|----------------------------------------------------------------------------------------------------------------|-----------------------------|----------------|----------------|--|

| RES             | DS(28:13) | Reserved                                                                                                       | -                           |                |                |  |

| Chip<br>Version | DS(12:5)  | Chip identification number                                                                                     | "(                          | 0001 0001"> V  | 1A             |  |

| RES             | DS(4:2)   | Reserved                                                                                                       |                             | -              |                |  |

| TX_READY        | DS(1)     | TX_READY, see section [6.5.1]<br>0 $\rightarrow$ Transmitter not Ready<br>1 $\rightarrow$ Transmitter is Ready |                             | -              |                |  |

| RES             | DS(0)     | Reserved -                                                                                                     |                             |                |                |  |

Table 12 Status Read-Only Parameters

#### 5.6. Recovery Command

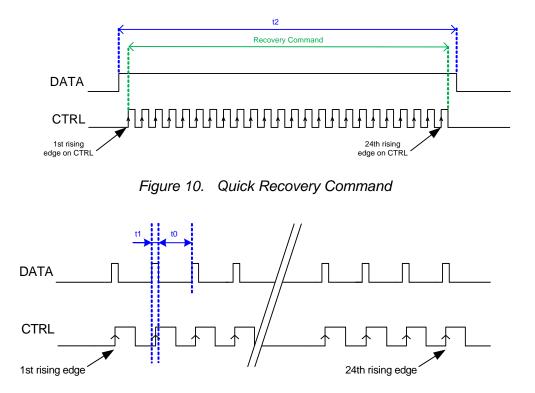

In the event of spurious activity (less than 24 clock cycles received) on the CTRL pin, control over the TWI interface can be recovered in two possible ways:

Figure 11. Pulsed Recovery Command

- Notes If t2 < 5 us, the SX1243 will not turn into Tx mode during the recovery command (if not previously in Tx mode)

- If t1 < 5 us, with t0 > 5 us, the SX1243 will not turn into Tx mode in the second scenario of recovery command

- During the Pulsed recovery command, t0 timing does not have any upper limit

- If t1 or t2 exceeds 5us, the recovery command will still be successful, but the transmitter will momentarily turn on

### 6. Application Information

#### 6.1. Crystal Specification

The SX1243 is designed to operate with a low-cost 22, 24 or 26 MHz crystal

Table 13

SX1243 Quartz Crystal Reference Oscillator Specification

| Symbol | Description                  | Min | Тур    |        | Max    | Unit |      |

|--------|------------------------------|-----|--------|--------|--------|------|------|

| FXOSC  | Crystal Frequency            | -   | 22     | 24     | 26     | -    | MHz  |

| LM     | Crystal Motional Inductance  | -   | 14.970 | 13.700 | 12.655 | -    | mH   |

| СМ     | Crystal Motional Capacitance | -   | 3.495  | 3.209  | 2.962  | -    | fF   |

| RS     | Crystal Serial Resistance    | -   |        | 20     |        | 100  | Ohms |

| C0     | Crystal Shunt Capacitance    | -   | 1.0    |        | 7.0    | pF   |      |

| CL     | Load Capacitance             | -   |        | 15     |        | -    | pF   |

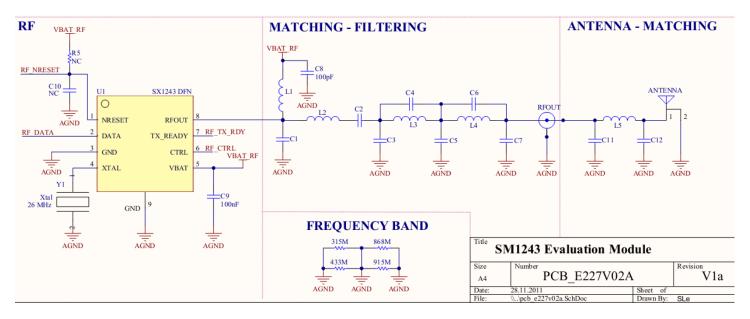

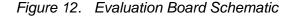

### 6.2. Evaluation Module

The evaluation module, presented in Figure 12, allows for the seamless evaluation of the SX1243 circuit. Several BOM options are offered to evaluate the performance in all frequency bands.

## SX1243 Integrated Transmitter IC

DATASHEET

The SX1243 reference design uses a tiny footprint of 16 x 6 mm, allowing for compact implementations on 2-layer PC Boards.

Figure 13. Evaluation Board Layout Top, Bottom Views

The following BOMs guarantee that the SX1243 product will be able to meet all regional regulatory requirements, with significant margin (more than 10dB) on the rejection of harmonics and spurs.

| Usage                                 | Label | 350 MHz           | 433 MHz | 868 MHz | 915 MHz<br>@+10dBm | 915 MHz<br>@0dBm | Туре     | Tolerance          |

|---------------------------------------|-------|-------------------|---------|---------|--------------------|------------------|----------|--------------------|

|                                       | L1    | 120nH             | 120nH   | 22nH    | 22nH               | 22nH             |          |                    |

|                                       | L2    | 39nH              | 33nH    | 12nH    | 12nH               | 12nH             | LQG15xxx |                    |

| Ъб                                    | L3    | 15nH              | 15nH    | 4.7nH   | 6.8nH              | 6.8nH            |          |                    |

| PA Matching and<br>Harmonic Filtering | L4    | 0 Ohm             | 0 Ohm   | 8.2nH   | 0 Ohm              | 6.8nH            |          |                    |

| Filt                                  | C1    | 2.2pF             | 0.5pF   | -       | 0.5pF              | 0.5pF            |          | Standard tolerance |

| ichi                                  | C2    | 100pF             | 100pF   | 33pF    | 18pF               | 18pF             |          |                    |

| Mat                                   | C3    | 8.2pF             | 8.2pF   | 1.8pF   | 5.6pF              | 5.6pF            |          |                    |

| A N<br>arm                            | C4    | 3.3pF             | 2.2pF   | 1.5pF   | -                  | -                | NPO      |                    |

| ΔĨ                                    | C5    | 8.2pF             | 8.2pF   | 1.8pF   | 2.2pF              | 2.2pF            |          |                    |

|                                       | C6    | -                 | -       | 18pF    | -                  | 18pF             |          |                    |

|                                       | C7    | -                 | -       | -       | -                  | -                |          |                    |

| Decoupling                            | C8    | 100pF             | 100pF   | 100pF   | 100pF              | 100pF            | NPO      |                    |

|                                       | C9    | 100nF             | 100nF   | 100nF   | 100nF              | 100nF            | X7R      |                    |

| Delayed                               | R5    | -                 | -       | -       | -                  | -                | -        |                    |

| POR                                   | C10   | -                 | -       | -       | -                  | -                | -        |                    |

| Antenna                               | L5    |                   |         |         |                    |                  |          |                    |

| Match                                 | C11   | Antenna dependant |         |         |                    |                  |          |                    |

| Match                                 | C12   |                   |         |         |                    |                  |          |                    |

| Inductor count                        |       | 3                 | 3       | 4       | 3                  | 4                |          |                    |

| Capacitor count                       |       | 7                 | 7       | 7       | 6                  | 7                |          |                    |

| Resistor count                        |       | 1                 | 1       | 0       | 1                  | 0                |          |                    |

Figure 14. Evaluation Board BOMs

#### WIRELESS & SENSING

Notes - The matching centered at 350 MHz offers a flat performance from 315 to 390 MHz, but could be modified to slightly improve efficiency at any frequency inbetween

- The 915 MHz @10dBm BOM is dedicated to systems running under CFR Part 15.247, either Frequency Hopping Spread Spectrum or Digital Modulation Techniques operation

- The 915 MHz @0dBm BOM is dedicated to systems running under CFR Part 15.249

### 6.3. NRESET Pin

When required, the pin NRESET can be controlled externally, to allow for:

- either a delayed Power On Reset (POR) cycle of the SX1243, allowing for the companion micro to reset and assign its port directions. This is achieved by connecting a R/C time constant to the NRESET pin.

- or an On-the-go Reset of the SX1243 at any moment in time, if required by the application. This is achieved by pulling the NRESET pin low for more than 100 microseconds, then releasing it to high impedance (normal termination).

#### 6.4. TX\_READY Pin

For timing critical applications, TX\_READY pin can be useful to know precisely when the transmitter is ready for operation and therefore save energy. As an option TX\_READY can be connected to inform the companion device that the PA ramp up phase has been terminated, hence the SX1243 is ready for data transmission.

#### 6.5. Low Power Optimization

The SX1243 is designed to reduce the cost of the RF transmitter functionnality. To this end, a single DATA signal can be enough to operate the transmitter, in any of the two Power & Go modes. In this situation, TS\_START and TOFFT timings, tabulated in Section 2.4, must be respected, leading to significant periods of time during which the transmitter is On and no valuable information is transmitted.

For more demanding applications where energy usage is critical, the SX1243 offers hardware and software support to accurately control the transmitter On time, and therefore save energy:

#### 6.5.1. 2 Connections: CTRL, DATA

If the two signals of the TWI interface can be controlled by the host microcontroller, Tx On time and energy usage can be optimized as follows:

- At the device turn on, instead of waiting for TS\_TR (2ms max, but XTAL dependant), the status flag TX\_READY can be polled on the TWI interface. As soon as the TX\_READY flag is set, the microcontroller can start toggling DATA to transmit the useful packet. This method is only valid in Forced Tx mode.

- At the device turn off, the user can immediately turn off the transmitter after the transmission of packet, assuming that the Forced Transmit mode was used.

#### 6.5.2. 3 Connections: CTRL, DATA, TX\_READY

In applications where the number of connections between the microcontroller and the RF chip is less critical, TX\_READY pin can be connected to either a GPIO port, or an external interrupt port of the micro. The two optimizations described in the former subsection will also be possible.

### 7. SX1243 Packaging

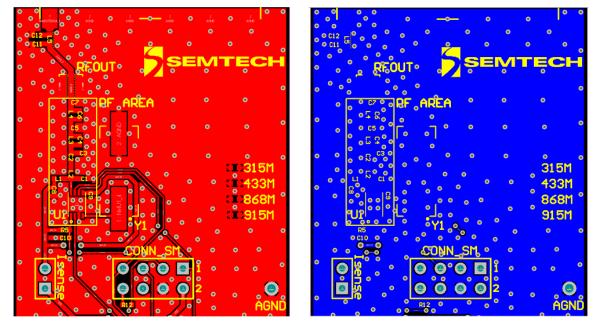

#### 7.1. Package Outline Drawing

Figure 15. Package Outline Drawing

#### 7.2. Thermal Impedance

The thermal impedance of this package, calculated from a package in still air, on a 4-layer FR4 PCB, as per the Jedec standard, is Theta ja = 67 °C/W typ.

### DATASHEET

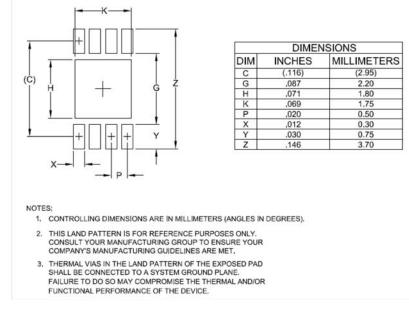

#### 7.3. Land Pattern

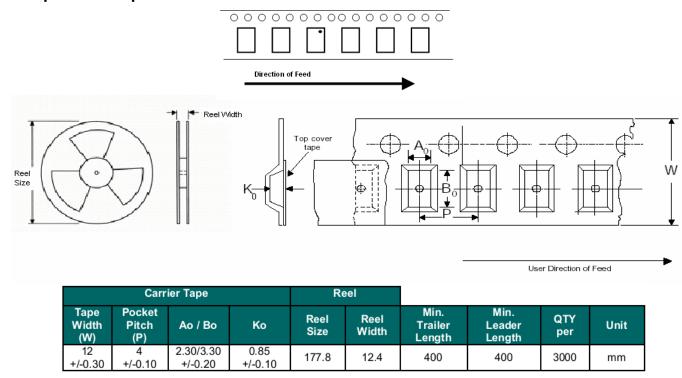

#### 7.4. Tape & Reel Specification

Figure 17. Tape & Reel Specification, DFN Package

### 8. Revision History

Table 14 Revision History

| Revision | Date          | Comment                                                                                                                                                                                         |  |  |  |

|----------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1        | January 2012  | First FINAL release                                                                                                                                                                             |  |  |  |

| 2        | February 2012 | Add Tape and Reel specification<br>Add Minimum Order Quantity<br>Add Thermal Impedance of the package<br>Add digital pins specifications<br>Typographical corrections<br>Modify section [6.5.1] |  |  |  |

| 3        | May 2012      | Adjust Electrical specifications                                                                                                                                                                |  |  |  |

| 4        | January 2013  | Add Marking Diagram                                                                                                                                                                             |  |  |  |

#### © Semtech 2013

All rights reserved. Reproduction in whole or in part is prohibited without the prior written consent of the copyright owner. The information presented in this document does not form part of any quotation or contract, is believed to be accurate and reliable and may be changed without notice. No liability will be accepted by the publisher for any consequence of its use. Publication thereof does not convey nor imply any license under patent or other industrial or intellectual property rights. Semtech assumes no responsibility or liability whatsoever for any failure or unexpected operation resulting from misuse, neglect improper installation, repair or improper handling or unusual physical or electrical stress including, but not limited to, exposure to parameters beyond the specified maximum ratings or operation outside the specified range.

SEMTECH PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF SEMTECH PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE UNDERTAKEN SOLELY AT THE CUSTOMER'S OWN RISK. Should a customer purchase or use Semtech products for any such unauthorized application, the customer shall indemnify and hold Semtech and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs damages and attorney fees which could arise.

#### Contact information

#### Semtech Corporation WIRELESS & SENSING Products

|          | E-mail: sales@semtech.com Internet: http://www.semtech.com                                                   |

|----------|--------------------------------------------------------------------------------------------------------------|

| USA      | 200 Flynn Road, Camarillo, CA 93012-8790.<br>Tel: +1 805 498 2111 Fax: +1 805 498 3804                       |

| FAR EAST | 12F, No. 89 Sec. 5, Nanking E. Road, Taipei, 105, TWN, R.O.C.<br>Tel: +886 2 2748 3380 Fax: +886 2 2748 3390 |

| EUROPE   | Semtech Neuchâtel, Gouttes d'Or 40, 2000 Neuchatel<br>Tel: +41 32 729 4000 Fax +41 32 729 4001               |