# CC/CV Mode Synchronous Step-Down Converter

#### **DESCRIPTION**

The EUP3270 is a synchronous step-down converter capable of driving 4A continuous load with excellent line and load regulation. The EUP3270 operates in either CC (Constant Current) mode or CV (Constant Voltage) mode with an input voltage range from 4.5V to 30V. The EUP3270 provides programmable cable compensation by adjusting external resistor divider. External shutdown function can be controlled by pulling COMP pin to a level below 0.14V.

Fault protection includes secondary cycle-by-cycle current limit, short circuit protection and thermal shutdown. Internal soft-start minimizes the inrush supply current and the output overshoot at initial startup.

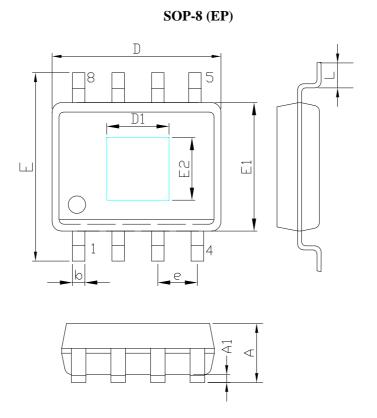

The EUP3270 is available in SOP-8 (EP) package.

#### **FEATURES**

- 4.5V to 30V Wide Input Operating Range

- 80kHz~800kHz Switching Frequency Selection

- CC/CV Mode Control

- Up to 4A Output Current

- +/- 1.5% Voltage Reference Accuracy

- +/- 4% Constant Current Accuracy

- Programmable Cable Compensation

- Internal Soft Start

- Single Pin to External Compensation and Shutdown Control

- Hiccup Short Circuit Protection

- Secondary Cycle-by-Cycle Current Limit

- Thermal Shutdown

- Available in SOP-8 (EP) Package

- RoHS Compliant and 100% Lead(Pb)-Free Halogen-Free

#### **APPLICATIONS**

- Car Charger

- Portable charger applications

- DC/DC converters with current limited

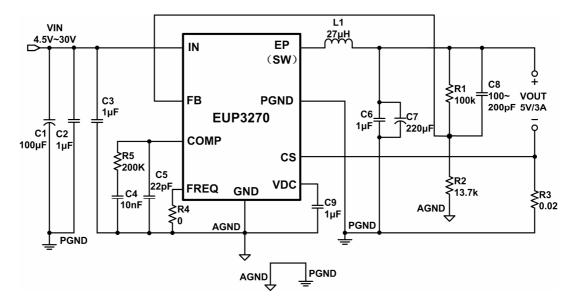

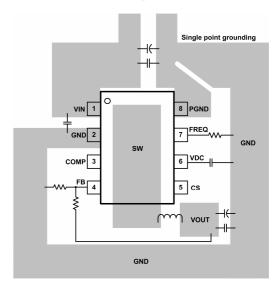

#### **Typical Application Circuit**

Figure 1. 150KHz Operating Frequency Application Circuit

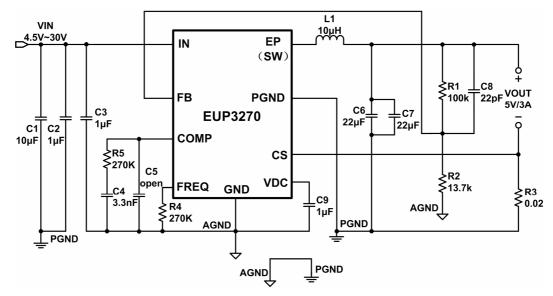

# **Typical Application Circuit (continued)**

Figure 2. 340KHz Operating Frequency Application Circuit

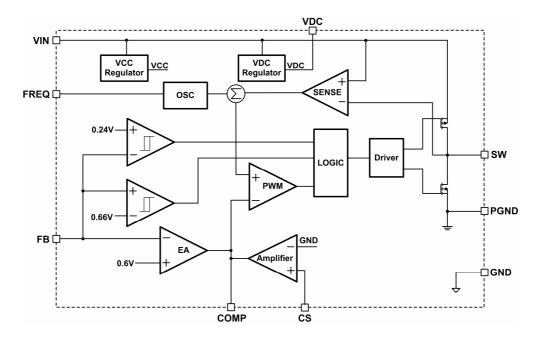

# **Block Diagram**

Figure 3. Functional Block Diagram

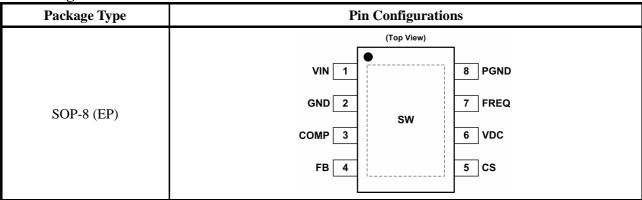

EUTECH MICROELECTRONICS **Pin Configurations**

# **Pin Description**

| Pin Name | SOP-8 (EP) | DESCRIPTION                                                                    |  |  |  |

|----------|------------|--------------------------------------------------------------------------------|--|--|--|

| VIN      | 1          | Input Supply Pin.                                                              |  |  |  |

| GND      | 2          | Ground.                                                                        |  |  |  |

| COMP     | 3          | Loop compensation pin. Drive COMP voltage logic low to turn off the converter. |  |  |  |

| FB       | 4          | Output Feedback Input.                                                         |  |  |  |

| CS       | 5          | Current sense input pin.                                                       |  |  |  |

| VDC      | 6          | Internal VDC regulator output. Bypass VDC to ground with a ceramic capacitor.  |  |  |  |

| FREQ     | 7          | Frequency select pin.                                                          |  |  |  |

| PGND     | 8          | Power ground.                                                                  |  |  |  |

| SW       | EP         | Power switch pin.                                                              |  |  |  |

DS3270 Ver1.3 Dec. 2016

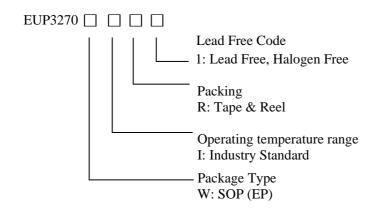

# **Ordering Information**

| Order Number | Package Type | Marking        | Quantity per Reel | <b>Operating Temperature Range</b> |

|--------------|--------------|----------------|-------------------|------------------------------------|

| EUP3270WIR1  | SOP-8 (EP)   | xxxxx<br>P3270 | 2500              | -40°C to +85°C                     |

### **Absolute Maximum Ratings (1)**

|   | Input Voltage (V <sub>IN</sub> )              | -0.3V to 32V          |

|---|-----------------------------------------------|-----------------------|

| • | Switch Voltage (V <sub>SW</sub> )             | -1V to $V_{IN}$ +0.3V |

| • | CS                                            | -0.3V to 13V          |

| • | All Other Pins                                | -0.3V to 6V           |

| • | Junction Temperature                          | 150°C                 |

| • | Storage Temperature                           | -65°C to +150°C       |

| • | Lead Temp(Soldering, 10sec)                   | 260°C                 |

| • | Thermal Resistance θ <sub>JA</sub> (SOP-8_EP) | 60°C /W               |

|   |                                               |                       |

## **Recommend Operating Conditions (2)**

- Supply Voltage ( $V_{IN}$ ) ------ 4.5V to 30V

Note (1): Stress beyond those listed under "Absolute Maximum Ratings" may damage the device.

Note (2): The device is not guaranteed to function outside the recommended operating conditions.

#### **Electrical Characteristics**

$(V_{IN}=12V, T_A=+25$ °C,  $I_{OUT}=2.0A$ , unless otherwise specified)

| Parameter                                        |                            | Conditions                  | EUP3270 |      |       | Unit      |  |

|--------------------------------------------------|----------------------------|-----------------------------|---------|------|-------|-----------|--|

| rarameter                                        | Conditions                 | Min.                        | Typ.    | Max. | UIII  |           |  |

| Input voltage                                    |                            | 4.5                         |         | 30   | V     |           |  |

| Input No Load Current                            |                            | I <sub>OUT</sub> =0A        |         |      | 10    | mA        |  |

| Quiescent Current                                |                            | $V_{FB}=0.8V$               |         | 1    |       | mA        |  |

| Shutdown Current                                 |                            | $V_{COMP}=0V$               |         | 380  |       | μΑ        |  |

| Input Under Voltage Lockout Three                | eshold Rising              |                             | 3.95    | 4.15 | 4.35  | V         |  |

| Input Under Voltage Lockout Three                | eshold Hysteresis          |                             |         | 0.4  |       | V         |  |

| Current Limit                                    |                            |                             |         | 7.5  |       | A         |  |

| Operating frequency                              | R4=0Ω                      |                             | 135     | 150  | 165   | kHz       |  |

| Operating frequency                              | K4=052                     | $T_J = -25$ °C to $125$ °C  | 127     |      | 173   | kHz       |  |

| Maximum Duty Cycle                               |                            |                             |         |      | 100   | %         |  |

| Minimum On-Time                                  |                            |                             |         | 150  |       | ns        |  |

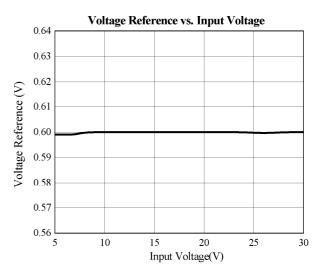

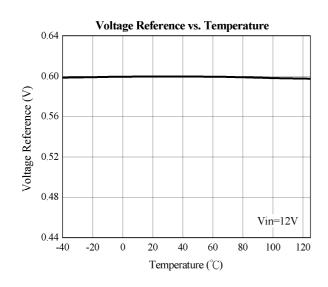

| Reference Voltage of the Voltage Error Amplifier |                            |                             | 0.591   | 0.6  | 0.609 | V         |  |

| CS Reference Voltage                             |                            |                             | 57.4    | 60   | 62.6  | mV        |  |

| C5 Reference voltage                             |                            | $T_J = -25$ °C to $125$ °C  | 56.4    |      | 63.6  | mV        |  |

| Transconductance of Error Ampli                  |                            |                             | 75      |      | μA/V  |           |  |

| Reference Voltage of the Short Ci                |                            |                             | 0.24    |      | V     |           |  |

| Comparator                                       |                            |                             | *       |      | ٧     |           |  |

| COMP Enable Threshold Rising                     |                            |                             | 0.14    |      | V     |           |  |

| COMP Enable Threshold Hystere                    |                            |                             | 40      |      | mV    |           |  |

| Thermal Shut-down Temperature                    |                            | Temperature Rising          |         | 150  |       | °C        |  |

|                                                  |                            | Temperature Falling         |         | 100  |       | °C        |  |

| PMOS Drain-Source On-State Resistance            |                            | $V_{IN}=12V$ , $I_{OUT}=1A$ |         | 35   |       | mΩ        |  |

| 1 WOS Diani-Source Oil-State Re                  | $V_{IN}=5V$ , $I_{OUT}=1A$ |                             | 44      |      |       |           |  |

| NMOS Drain-Source On-State Resistance            |                            | I <sub>OUT</sub> =1A        |         | 32   |       | $m\Omega$ |  |

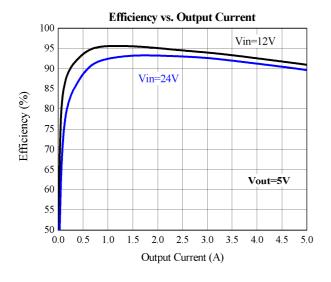

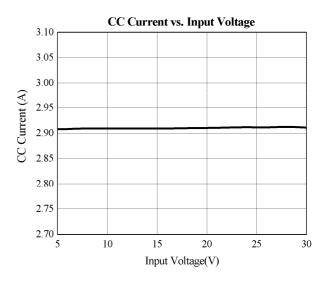

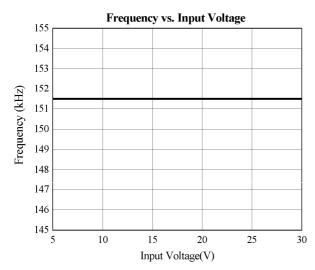

## **Typical Operating Characteristics**

$V_{IN}$ =12V,  $V_{OUT}$ =5V,  $F_{SW}$ =150KHz,  $T_A$ =25°C, unless otherwise noted.

EUTECH

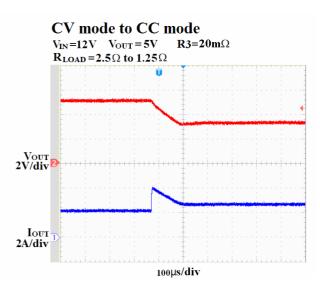

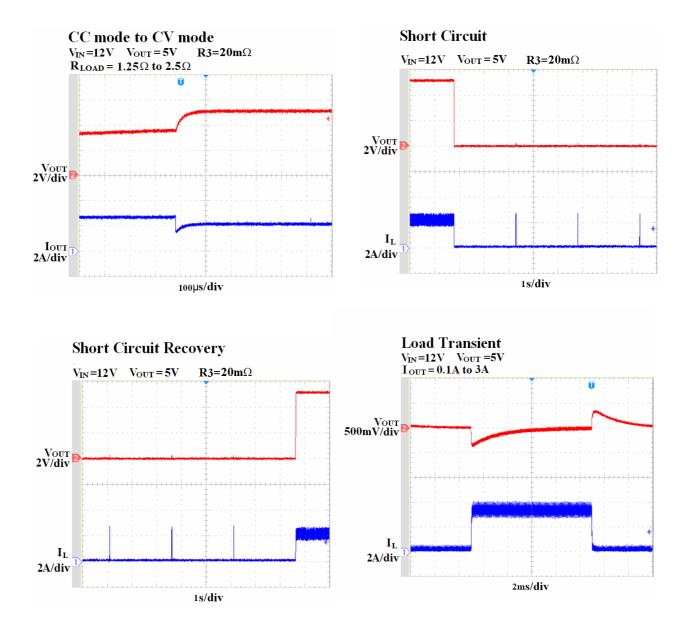

## **Typical Operating Characteristics (continued)**

$V_{IN}$ =12V,  $V_{OUT}$ =5V,  $F_{SW}$ =150KHz,  $T_A$ =25°C, unless otherwise noted.

#### **Functional Description**

The EUP3270 is a current-mode synchronous step-down converter with 4.5V to 30V input power supply. The device can provide up to 4A continuous current to the output. The EUP3270 uses current-mode architecture to control the regulator loop. The output voltage is measured at FB through a resistive voltage divider and amplified through the internal error amplifier. The output current of the transconductance error amplifier is presented at COMP pin where a RC network compensates the regulator loop. Slope compensation is internally added to eliminate subharmonic oscillation at high duty cycle. The slope compensation adds voltage ramp to the inductor current signal which reduces maximum inductor peak current at high duty cycles.

#### CC/CV mode control

The EUP3270 operates in either CC mode or CV mode. The CV mode regulates the output voltage. When output current reaches the CC threshold, the device enters CC mode to limit the output current.

#### **Programmable cable compensation**

The EUP3270 provides programmable cable compensation by adjusting the external resistor divider to compensate resistive voltage drop across the charger's output cable.

#### **Internal soft-start**

Internal soft-start minimizes the inrush supply current and the output overshoot at initial startup.

#### **Short circuit protection**

The EUP3270 provides the output short circuit protection function to prevent large output short circuit current from damaging the device. When output short happens, the device shuts down and returns to normal operation automatically when the short circuit condition is released.

#### Thermal Shutdown

The EUP3270 stops switching when its junction temperature exceeds 150°C and resumes when the temperature has dropped by 50°C to protect the device.

#### **Application Information**

The output voltage is set through a resistive voltage divider and can be expressed by the equation as follows

$$V_{OUT} = 0.6V \times (R1 + R2) / R2$$

#### **Setting the CC current**

EUP3270 constant current value is set by the resistor R3 connected between the CS and GND pins. The CC current is determined by the equation as follows

$$I_{cs} = 0.06 V / R3$$

#### Setting the switching frequency

The switching frequency is set by the resistor R4 connected between the FREQ and GND pins and can be expressed by the equation as follows

$$f_{sw} = 10^{11} / R4$$

The switching frequency is 150kHz when R4= $0\Omega$ .

#### Setting the cable compensation

The EUP3270 provides programmable cable voltage drop compensation using the impedance at the FB pin to compensate voltage drop across the charger's output cable. The cable compensation voltage can be expressed

$$\Delta V_{OUT} = 38\mu \times (I_{OUT} \times R3) \times R1$$

By adjust the value of R1, the cable compensation voltage can be programmed.

#### Lavout Considerations

Several layout tips below must be considered for the best electric performance.

- 1. Analog ground and power ground are to be kept separate and finally combined using single point grounding.

- 2. Input capacitors should be connected to the IN pin and the PGND pin as close as possible to reduce the switching spikes.

- 3. Keep the switching node (SW) away from sensitive small signal nodes. Keep traces to these nodes as short as possible and there should be no other weak signal traces in parallel with theses traces on any layer.

- 4. Voltage divider R1 and R2 should be placed as close as possible to FB and GND.

- 5. Compensation network components should be placed as close as possible to COMP and GND. Compensation resistor R5 should be 50K~270K according to different application.

- 6. Frequency setting resistor R4 should be placed between FREQ and GND.

- 7. Decoupling capacitor C9 should be connected to VDC and GND as close as possible.

Figure 4. Layout Guide

# **Packaging Information**

Remark: Exposed pad outline drawing is for reference only.

| SYMBOLS | MILLIMETERS |        |      | INCHES    |        |       |  |

|---------|-------------|--------|------|-----------|--------|-------|--|

| SIMBOLS | MIN.        | Normal | MAX. | MIN.      | Normal | MAX.  |  |

| A       | 1.35        | -      | 1.75 | 0.053     | -      | 0.069 |  |

| A1      | 0.00        | -      | 0.25 | 0.000     | -      | 0.010 |  |

| D       | 4.80        | 4.90   | 5.00 | 0.189     | 0.193  | 0.197 |  |

| E1      | 3.70        | 3.90   | 4.00 | 0.146     | 0.154  | 0.157 |  |

| D1      | 2.67        | 2.97   | 3.50 | 0.105     | 0.117  | 0.138 |  |

| E2      | 1.78        | 2.18   | 2.60 | 0.070     | 0.086  | 0.102 |  |

| Е       | 5.80        | 6.00   | 6.20 | 0.228     | 0.236  | 0.244 |  |

| L       | 0.40        | -      | 1.27 | 0.016     | -      | 0.050 |  |

| b       | 0.31        | -      | 0.51 | 0.012     | -      | 0.020 |  |

| e       | 1.27 REF    |        |      | 0.050 REF |        |       |  |

EUTECH MICROELECTRONICS