## Description

The P9222-R is an integrated single-chip wireless power receiver IC (Rx) for up to 5W applications. The device receives an AC power signal from a wireless power transmitter, such as the P9235A-RB WPC Qi BPP Wireless Transmitter IC, and converts it to a rectified output voltage, which can be used to power devices or supply the battery charger input in a wide range of wireless power applications. The receiver (Rx) integrates a high-efficiency synchronous full bridge rectifier (SFBR) and control circuits used to send message packets to the transmitter (Tx) in order to optimize power delivery.

The P9222-R is highly efficient at light loads and very well-suited for low-power applications such as earbuds case charging. A unique Ping detect feature gives the user an early indication of the wireless charger connection and improves thermal performance at the end of complete battery charging. Low under-voltage lockout (UVLO) threshold allows the receiver to start up even with a weaker digital ping strength signal from a transmitter over an extended area.

The device includes over-temperature and under/over-voltage protection. The internal over-voltage clamping protects the rectifier output from rising above the overvoltage level when the receiver is quickly moved from a low-coupling position to a high-coupling position. The integrated 32-bit ARM<sup>®</sup> Cortex<sup>®</sup>-M0 processor (trademark of ARM, Ltd.) offers a high level of programmability and design parameters that can be easily configured through the I<sup>2</sup>C interface or an external EEPROM.

The P9222-R is available in a RoHS ultra-small WLCSP-40 package and it is rated for a 0 to 85°C ambient operating temperature range.

## **Typical Applications**

Wireless power solutions for mobile solutions including:

- Wireless earbuds case charging

- Wearables and fitness trackers

- Mobile devices

- Hearing aids case charging

## Features

- Ultra-compact, efficient wireless power receiver for up to 5W applications

- WPC 1.2.4 Qi Baseline Power Profile (BPP) compatible

- Optimized light load efficiency for low power applications

- Ping detection for reduced power consumption at end of charging

- Low under-voltage lockout (UVLO) for low voltage start-up for faster connections over an extended area

- ASK and FSK modulation/demodulation for Bi-directional Communication: Rx-to-Tx and Tx-to-Rx

- Easy configuration of design parameters through I<sup>2</sup>C interface on an external EEPROM

- ADC input to measure battery voltage or system voltage

- Embedded 32-bit ARM<sup>®</sup> Cortex<sup>®</sup>-M0 processor

- Internal over-voltage clamping

- Low standby and operating mode power consumption

- High performance low dropout (LDO) regulator with low RDS(on) and programmable current limiting

- Supports I<sup>2</sup>C slave/master mode

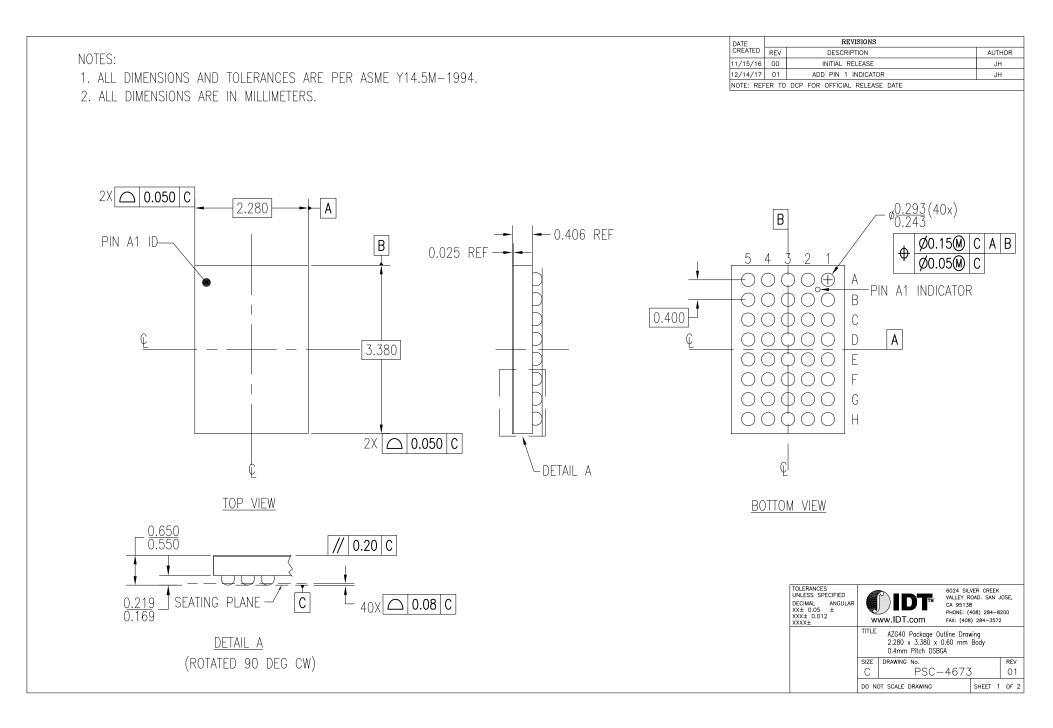

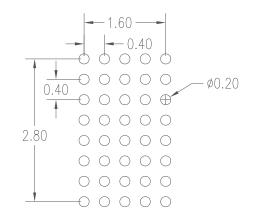

- 40-WLCSP: 5 × 8 ball array, 2.28 × 3.38 mm, 0.4mm pitch

## **Block Diagram**

# () IDT.

## Contents

| 1.  | Pin A | ssignments                                          | 7  |

|-----|-------|-----------------------------------------------------|----|

| 2.  | Pin D | Descriptions                                        | 8  |

| 3.  | Abso  | lute Maximum Ratings                                | 10 |

| 4.  | Therr | nal Characteristics                                 | 11 |

| 5.  | Elect | rical Characteristics                               | 12 |

| 6.  | Desc  | ription of the Wireless Power Charging System       | 16 |

| 7.  | Туріс | al Performance Characteristics                      | 17 |

| 8.  | Theo  | ry of Operation                                     | 19 |

|     | 8.1   | Overview                                            | 19 |

|     |       | 8.1.1 Low-Power Ping Detection                      | 19 |

|     |       | 8.1.2 Rx Operation                                  | 19 |

|     | 8.2   | Wireless Power Control                              | 19 |

|     | 8.3   | Startup 19                                          |    |

|     | 8.4   | Power Transfer                                      | 20 |

|     | 8.5   | Synchronous Rectifier                               | 20 |

|     | 8.6   | Over-Voltage Protection                             | 20 |

|     | 8.7   | Over-Current Protection and Thermal Shutdown        | 20 |

|     | 8.8   | External Temperature Sensing                        | 20 |

|     | 8.9   | Rectifier and VRECT Level                           | 21 |

|     | 8.10  | Interrupt Output                                    | 21 |

|     | 8.11  | Low Drop-Out (LDO) Regulators                       | 22 |

|     | 8.12  | MLDO Output Enable Conditions                       | 22 |

|     | 8.13  | Output Power Options                                | 22 |

| 9.  | WPC   | Mode Characteristics                                | 23 |

|     | 9.1   | WPC-Compliant Power Transfer                        | 23 |

|     | 9.2   | Advanced Foreign-Object Detection (FOD) in WPC Mode | 23 |

|     | 9.3   | WPC Modulation/Communication                        | 23 |

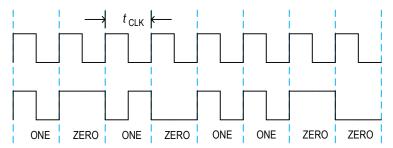

|     | 9.4   | Bit Encoding Scheme for ASK                         | 24 |

|     | 9.5   | System Feedback Control                             | 25 |

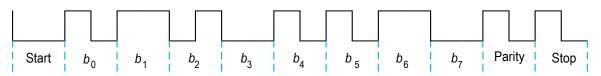

|     |       | 9.5.1 Selection                                     | 25 |

|     |       | 9.5.2 Ping                                          | 26 |

|     |       | 9.5.3 Identification and Configuration              |    |

|     |       | 9.5.4 Power Transfer                                | 26 |

| 10. | Appli | cations Information                                 |    |

|     |       | Receiver Coil                                       |    |

|     |       | Series and Parallel Resonant Capacitor Selection    |    |

|     | 10.3  | VRECT Pin                                           | 28 |

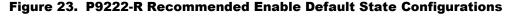

|     | 10.4  | Enable Pin                                          | 28 |

|     |       |                                                     |    |

|     | 10.5   | Transie    | nt Voltage Suppressor Diodes (TVS)                  | 28 |

|-----|--------|------------|-----------------------------------------------------|----|

|     | 10.6   | GPIO P     | ins                                                 | 29 |

|     |        | 10.6.1     | OD0 Pin                                             | 29 |

|     |        | 10.6.2     | OD1 Pin                                             | 29 |

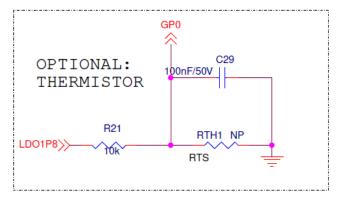

|     |        | 10.6.3     | OD2 Pin                                             | 29 |

|     |        | 10.6.4     | GP0 Pin                                             | 29 |

|     |        | 10.6.5     | GP1 Pin                                             | 29 |

|     |        | 10.6.6     | GP2 Pin                                             | 30 |

|     | 10.7   | Low-Po     | wer Ping Detection Operation                        | 30 |

|     | 10.8   | Configu    | ration of P9222-R Parameters                        | 32 |

|     | 10.9   | P9222-I    | R Internal Register Access by Application Processor | 32 |

|     | 10.10  | ) Externa  | I EEPROM Access by P9222-R                          | 32 |

| 11. | Exam   | ples of L  | lser Customizing P9222-R Operating Parameters       | 33 |

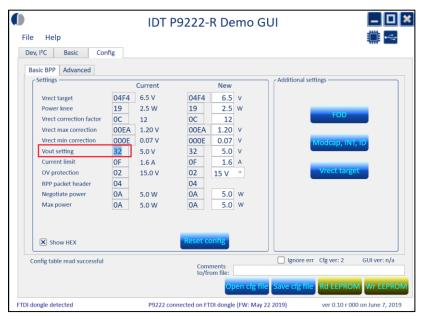

|     | 11.1   | LDO Ou     | Itput Voltage (VOUT) Configuration                  | 33 |

|     |        | 11.1.1     | VOUT Adjustment via the I2C Interface               | 33 |

|     |        | 11.1.2     | VOUT Configuration Change Using an External EEPROM  | 34 |

|     | 11.2   | Current    | Limit (ILIM) Configuration                          | 34 |

|     | 11.3   | Overvol    | tage (OV) Protection Configuration                  | 35 |

|     | 11.4   | FOD (F     | oreign Object Detection)                            | 35 |

|     |        | 11.4.1     | Configuring FOD Parameters                          | 36 |

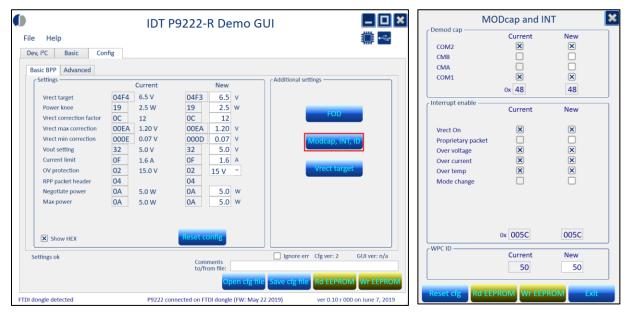

|     |        | 11.4.2     | Modulation Capacitor and Interrupt Enables          | 37 |

| 12. | I2C F  | unction    |                                                     | 38 |

| 13. | List o | f Registe  | rs                                                  | 38 |

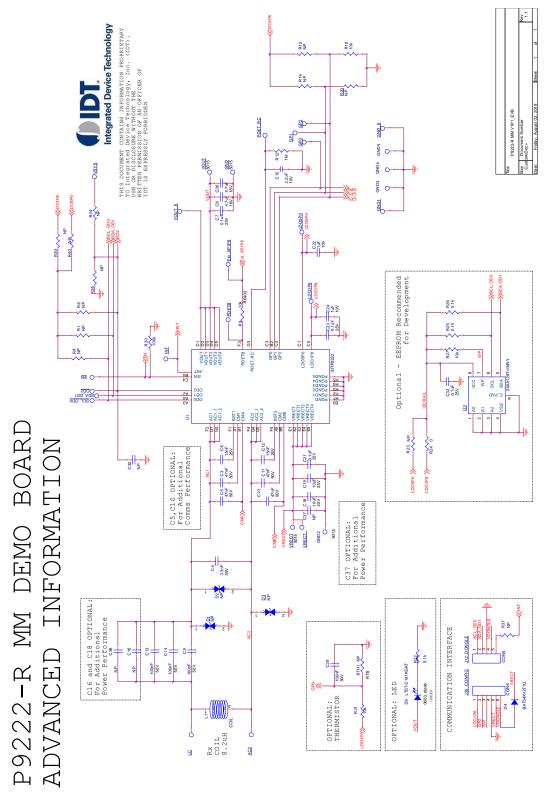

| 14. | Appli  | cation Sc  | hematic                                             | 48 |

| 15. | Packa  | age Outli  | ne Drawings                                         | 49 |

| 16. | Marki  | ing Diagr  | am                                                  | 49 |

| 17. | Order  | ring Infor | nation                                              | 49 |

| 18. | Revis  | sion Histo | ry                                                  | 50 |

|     |        |            |                                                     |    |

## **List of Figures**

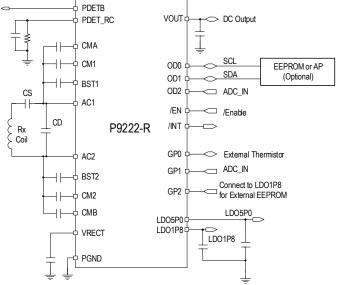

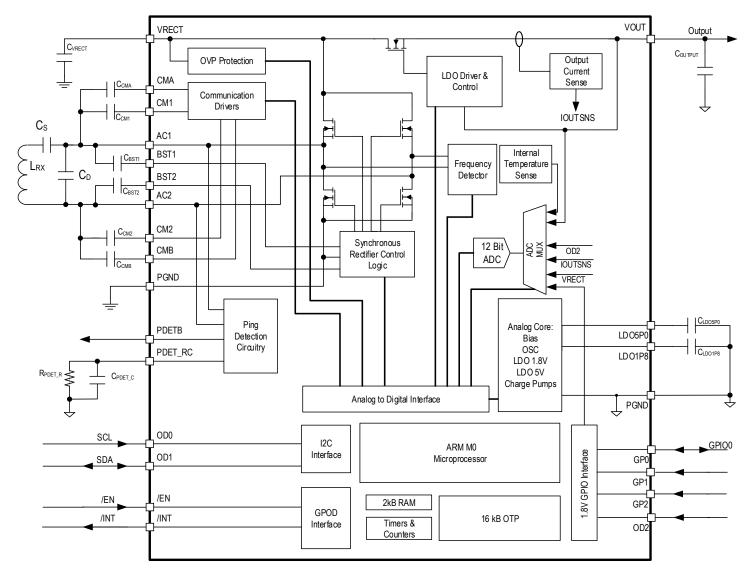

| Figure 1. | Simplified Block Diagram                                                         | 1  |

|-----------|----------------------------------------------------------------------------------|----|

| Figure 2. | P9222-R Block and Application Diagram                                            | 2  |

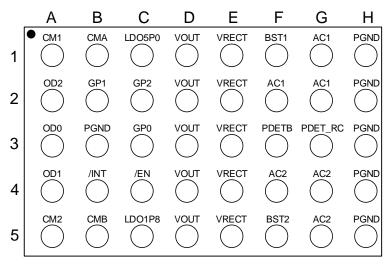

| Figure 3. | Pin Assignments for 40-WLCSP (AZG40), 2.28 × 3.38 mm with 0.4mm Pitch – Top View | 7  |

| Figure 4. | Block Diagram of WPC v1.2.4-Compliant Wireless Power Transfer System             | 16 |

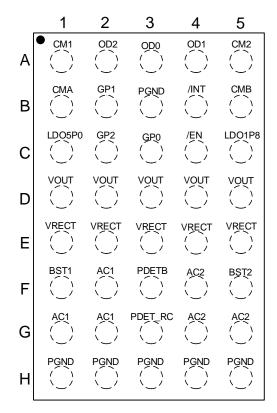

| Figure 5. | System Efficiency vs Output Current                                              | 17 |

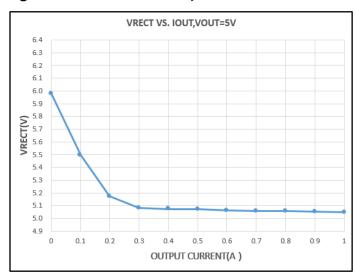

| Figure 6. | VRECT vs IOUT, Vout = 5.0V                                                       | 17 |

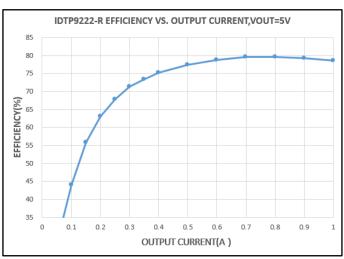

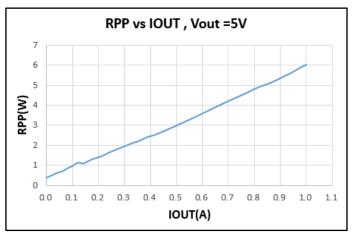

| Figure 7. | Reported Received Power (RPP) vs lout on NOK9 Transmitter                        | 17 |

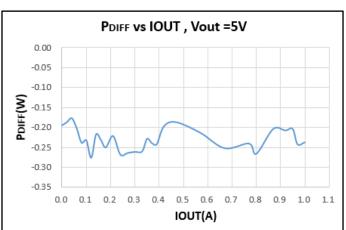

| Figure 8. | PDIFF (PTX-PRX) vs lout on NOK9 Transmitter                                      | 17 |

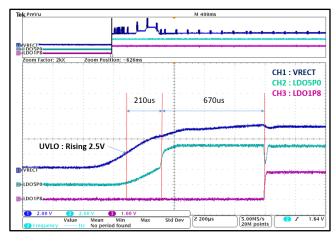

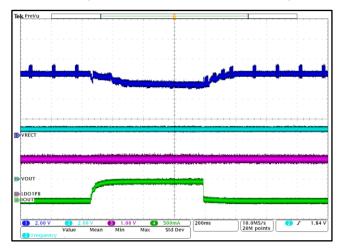

| Figure 9. | Initial Startup                                                                  | 18 |

# () IDT.

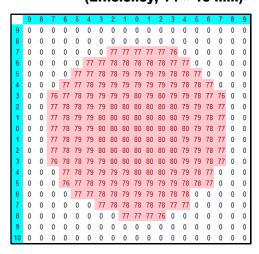

| Figure 10. A | Active Charging Area (Efficiency, 14 × 15 mm)                             | 18 |

|--------------|---------------------------------------------------------------------------|----|

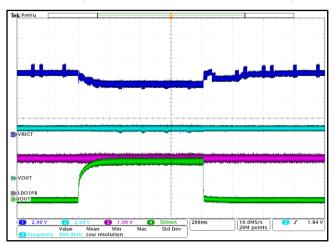

| Figure 11. I | Load Transient Response 1 (Vout = 5V, lout 0mA to 500mA)                  | 18 |

| Figure 12. L | Load Transient Response 2 (Vout = 5V, lout 0mA to 1000mA)                 | 18 |

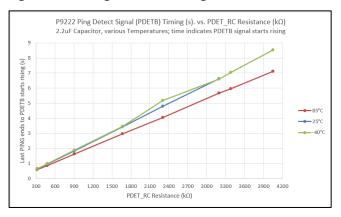

| Figure 13. F | Ping Detect Timing                                                        | 18 |

| Figure 14. A | AC Modulation (COM1)                                                      | 18 |

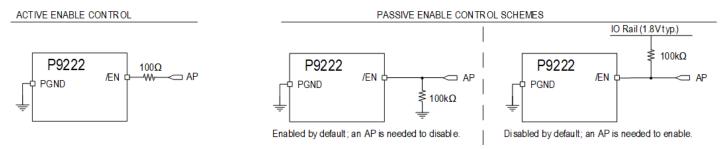

| Figure 15. F | RTH1 and R21 Schematic Location                                           | 21 |

| Figure 16. F | RTH1 and R21 PCB Location                                                 | 21 |

| Figure 17. F | Rx Modulation Components                                                  | 23 |

| Figure 18. ( | Communication Packet Structure                                            | 24 |

| Figure 19. \ | WPC Packet Example with Reference Clock Shown                             | 24 |

| Figure 20.   | Byte Encoding Scheme                                                      | 24 |

| Figure 21. \ | WPC System Feedback Control BPP Mode                                      | 25 |

| Figure 22.   | Dual Resonant Circuits with Receiver Coil                                 | 27 |

| Figure 23. F | P9222-R Recommended Enable Default State Configurations                   | 28 |

| Figure 24. ( | GP0 Pin External Connection to Thermistor Configuration                   | 29 |

| Figure 25. ( | GP2 Pin External Connections for External EEPROM Selection                | 30 |

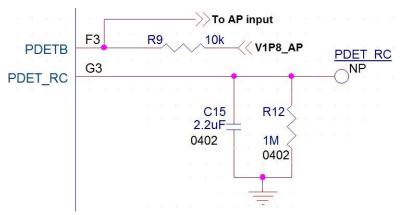

| Figure 26. F | Ping Detection – Typical Application Schematic Components and Connections | 30 |

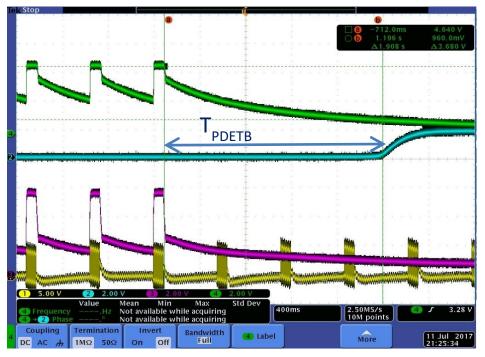

| Figure 27. F | P9222-R Ping Detect Waveforms                                             | 31 |

| Figure 28. \ | Writing to the Vout_Set Register using P9222-R Windows GUI                | 33 |

| Figure 29. ( | Changing the Default VOUT Value using the P9222-R Windows GUI             | 34 |

| Figure 30. ( | Changing the Default FOD Registers using the P9222-R Windows GUI          | 36 |

| Figure 31.   | Modulation and INT Settings Tab                                           | 37 |

| Figure 32. A | Applications Schematic                                                    | 48 |

|              |                                                                           |    |

## **List of Tables**

| Pin Descriptions                                                                    | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Absolute Maximum Ratings                                                            | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Thermal Characteristics for 40-WLCSP Package                                        | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| ESD Information                                                                     | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Recommended Coil Manufacturer                                                       | 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Recommended RC Values for PDET_RC Components Based on Capacitance and Ping Interval | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Recommended Maximum Estimated Power Loss                                            | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Chip Part Number ID Register, Chip_ID_L (0x00), Chip_ID_H (0x01)                    | 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Chip Revision Register, Chip_Rev (0x02)                                             | 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| OTP Firmware Revision Registers, OTP_FW_Major (0x04), OTP_FW_Minor (0x06)           | 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Status Registers, Status_L (0x34), Status_H (0x35)                                  | 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Interrupt Registers, INT_L (0x36), INT_H (0x37) <sup>[a]</sup>                      | 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Interrupt Enable Registers, INT_Enable_L (0x38), INT_Enable_H (0x39)                | 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                     | Absolute Maximum Ratings<br>Thermal Characteristics for 40-WLCSP Package<br>ESD Information<br>Electrical Characteristics<br>Recommended Coil Manufacturer<br>Recommended RC Values for PDET_RC Components Based on Capacitance and Ping Interval<br>Recommended Maximum Estimated Power Loss<br>Chip Part Number ID Register, Chip_ID_L (0x00), Chip_ID_H (0x01)<br>Chip Revision Register, Chip_Rev (0x02)<br>OTP Firmware Revision Registers, OTP_FW_Major (0x04), OTP_FW_Minor (0x06)<br>Status Registers, Status_L (0x34), Status_H (0x35)<br>Interrupt Registers, INT_L (0x36), INT_H (0x37) <sup>[a]</sup> |

# () IDT.

| Table 15. | Interrupt Clear Registers, INT_Clear_L (0x3A), INT_Clear_H (0x3B)                 | 40 |

|-----------|-----------------------------------------------------------------------------------|----|

| Table 16. | Vout Set Register, Vout_Set (0x3C)                                                | 41 |

| Table 17. | ILIM Set Register, ILIM_Set (0x3D)                                                | 41 |

| Table 18. | Battery Charge Status Register, CHG_Status (0x3E) <sup>[a]</sup>                  | 41 |

| Table 19. | End of Power Transfer Register, EPT (0x3F) <sup>[a]</sup>                         | 42 |

| Table 20. | Vrect ADC Value Registers, ADC_Vrect_L (0x40), ADC_Vrect_H (0x41)                 | 42 |

| Table 21. | Vout ADC Value Registers, ADC_Vout_L (0x42), ADC_Vout_H (0x43)                    | 42 |

| Table 22. | lout Value Registers, lout_L (0x44), lout_H (0x45)                                | 42 |

| Table 23. | Operating Frequency Registers, Op_Freq_L (0x48), Op_Freq_H (0x49) (RX Only)       | 42 |

| Table 24. | System Operating Mode Register, Sys_Op_Mode (0x4C)                                | 43 |

| Table 25. | (AP to P9222-R) Command Register, COM (0x4E)                                      | 43 |

| Table 26. | Die Temperature ADC Value Registers, ADC_Die_Temp_L (0x66), ADC_Die_Temp_H (0x67) | 44 |

| Table 27. | Overvoltage Protection Set Register (0xB3, 8-bit)                                 | 44 |

| Table 28. | ASK Modulation Depth Register (0xB2, 16-bit)                                      | 44 |

| Table 29. | Foreign Object Detection Registers, FOD (0x70-0x7E) <sup>[a]</sup>                | 45 |

| Table 30. | ADC Result Register (0xD4, 16-bit, OD2 in Default Config)                         | 45 |

| Table 31. | ADC Result Register (0xD6, 16-bit, GP1 in Default Config)                         | 46 |

| Table 32. | ADC Result Register (0xD8, 16-bit, GP2 in Default Config)                         | 46 |

| Table 33. | ADC Result Register (0xDA, 16-bit, Die Temperature in Default Config)             | 46 |

| Table 34. | External Thermistor Voltage on GP0 (0xB0, 16-bit)                                 | 46 |

| Table 35. | VRECT Target Register (0x90, 16-bit)                                              | 46 |

| Table 36. | VRECT Knee Register (0x92, 8-bit)                                                 | 47 |

| Table 37. | VRECT Correction Factor Register (0x93, 8-bit)                                    | 47 |

| Table 38. | VRECT Maximum Correction Register (0x94, 16-bit)                                  | 47 |

| Table 39. | VRECT Minimum Correction Register (0x96, 16-bit)                                  | 47 |

## 1. Pin Assignments

P9222-R CSP (Ball View)

P9222-R CSP (Top View)

## 2. Pin Descriptions

#### Table 1.Pin Descriptions

| Pin Number | Name               | Туре         | Description                                                                                                                                                                                                                                                                                                  |  |  |

|------------|--------------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| A1         | CM1                | Output       | High-voltage, open-drain output from the modulation FETs. Connect a 47nF capacitor from AC1 to CM1.                                                                                                                                                                                                          |  |  |

| A2         | OD2                | Input/Output | Open-drain GPIO. This pin is connected to the internal ADC and can measure voltages smaller than 1.2V. This pin can be left floating if not used.                                                                                                                                                            |  |  |

| A3         | OD0/SCL            | Input/Output | Open-drain GPIO. This pin supports an input of up to 5V, and is used for the I2C SCL connection. Connect this pin via a pull-up resistor to the system I/O supply. This pin can be left floating if not used.                                                                                                |  |  |

| A4         | OD1/SDA            | Input/Output | Open-drain GPIO. This pin supports an input of up to 5V, and is used for the I2C SDA connection. Connect this pin via a pull-up resistor to the system I/O supply. This pin can be left floating if not used.                                                                                                |  |  |

| A5         | CM2                | Output       | High-voltage, open-drain output from the modulation FETs. Connect a 47nF capacitor from AC2 to CM2.                                                                                                                                                                                                          |  |  |

| B1         | СМА                | Output       | High-voltage, open-drain output from the modulation FETs. By default, CMA capacitor is not used for communication. This pin can be left floating if not used.                                                                                                                                                |  |  |

| B2         | GP1/ADC<br>IN      | Input/Output | GPIO1. Pin is connected to internal ADC and can measure system voltage smaller than 1.8V. During startup this pin is set as a high-impedance. This pin can be left floating if not used.                                                                                                                     |  |  |

| B3, H1-H5  | PGND               | GND          | Power and logic ground.                                                                                                                                                                                                                                                                                      |  |  |

| B4         | /INT               | Output       | nterrupt output pin. Connect this pin to the application processor (AP) I/O voltage rail using an external pull-up resistor. The P9222-R drives this pin LOW to notify the AP host of status changes.                                                                                                        |  |  |

| B5         | СМВ                | Output       | High-voltage, open-drain modulation FETs. By default, CMB capacitor is not used for communication. This pin can be left floating if not used.                                                                                                                                                                |  |  |

| C1         | LDO5P0             | Output       | Internal 5V LDO for chip power only. Connect a 1µF and 0.1µF capacitor to ground.                                                                                                                                                                                                                            |  |  |

| C2         | GP2                | Input        | GPIO2. If this pin is pulled high to the internal 1.8V LDO (LDO1P8) using a 10K resistor, the P9222-R becomes an I2C master during startup to load 100 bytes of user configuration from external EEPROM. If this pin is pulled to ground, the P9222-R loads the default configuration from the internal OTP. |  |  |

| C3         | GP0/<br>Thermistor | Input/Output | GPIO0. This pin can be used to measure coil temperature. The P9222-R interrupts the processor when the coil voltage goes below 0.6V. During the startup this pin is set as a high-impedance. Pull this pin to 1.8V with a resistor if not used.                                                              |  |  |

| C4         | /EN                | Input        | Active-LOW enable pin. To enable the P9222-R, pull this pin to GND. To disable the P9222-R, pull this pin High.                                                                                                                                                                                              |  |  |

| C5         | LDO1P8             | Output       | Internal 1.8V LDO output for logic power. Connect a $1\mu$ F and $0.1\mu$ F capacitor to ground.                                                                                                                                                                                                             |  |  |

| D1-D5      | VOUT               | Output       | Main LDO output pin. Connect at least a 1×10µF capacitor from this pin to ground. It is not recommended to directly connect the USB charging port or other voltage sources to these pins. Back-to-back isolation FETs are recommended.                                                                       |  |  |

| E1-E5      | VRECT              | Input/Output | Filter capacitor for the internal rectifier. Capacitance requirements: Connect $2 \times 10 \mu$ F and $1 \times 0.1 \mu$ F capacitors in parallel from this pin to ground.                                                                                                                                  |  |  |

| Pin Number | Name                                          | Туре   | Description                                                                                                                                                                                                                                                                                                                                  |

|------------|-----------------------------------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| F1         | BST1                                          | Output | Bootstrap capacitor for driving the high side NFETs of the internal rectifier. Connect a 15nF capacitor from AC1 to BST1.                                                                                                                                                                                                                    |

| F2, G1, G2 | AC1                                           | Input  | AC power input 1. Connect AC1 to the Cs capacitors and Cs to the Rx coil. Connect the CD capacitor from AC1 to AC2 (see Figure 2 and the application schematic in Figure 32). Due to symmetry, the AC1 and AC2 connections are interchangeable.                                                                                              |

| F3         | PDETB                                         | Output | Open-drain, active-LOW. This pin is an output for indicating ping events are being received by the Rx. Connect this pin to the application processor (AP) I/O voltage rail using an external pull-up resistor.                                                                                                                               |

| F4, G4, G5 | AC2                                           | Input  | AC power input 2. Connect this pin to the Rx coil and the $C_D$ capacitor (see Figure 2) Due to symmetry, the AC1 and AC2 connections are interchangeable.)                                                                                                                                                                                  |

| F5         | BST2                                          | Output | Bootstrap capacitor for driving the high-side NFETs of the internal rectifier. Connect a 15nF capacitor from AC2 to BST2.                                                                                                                                                                                                                    |

| G3         | the AP if the Rx device is removed from the p |        | Ping-detect input pin for determining when PDETB will be de-asserted. This pin is used to notify the AP if the Rx device is removed from the power transfer interface. Connect an RC time-delay circuit designed to hold the voltage on this pin above V <sub>PDET_RC_IL</sub> between each Tx ping after power transfer is completed (EOC). |

## 3. Absolute Maximum Ratings

The absolute maximum ratings are stress ratings only. Stresses greater than those listed below can cause permanent damage to the device. Functional operation of the P9222-R at the absolute maximum ratings is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

Table 2. Absolute Maximum Ratings

| Parameter                                   | Conditions | Minimum <sup>[a]</sup> | Maximum <sup>[a]</sup> | Units |

|---------------------------------------------|------------|------------------------|------------------------|-------|

| VRECT, AC1, AC2, CMA, CMB, CM1, CM2         |            | -0.3                   | 20                     | V     |

| PDETB, PDET_RC, LDO5P0, OD[2:0]             |            | -0.3                   | 6                      | V     |

| LDO1P8, GP[2:0], /INT, /EN                  |            | -0.3                   | 2                      | V     |

| BST1                                        |            | AC1 – 0.3              | AC1 + 6                | V     |

| BST2                                        |            | AC2 – 0.3              | AC2 + 6                | V     |

| VOUT                                        |            | -0.3                   | 13                     | V     |

| PGND                                        |            | -0.3                   | 0.3                    | V     |

| Maximum RMS Current from CMA, CMB, CM1, CM2 |            |                        | 500                    | mA    |

| Maximum RMS Current from AC1, AC2           |            |                        | 2                      | А     |

[a] All voltages are referenced to ground unless otherwise noted.

## 4. Thermal Characteristics

#### Table 3. Thermal Characteristics for 40-WLCSP Package

| Symbol | Parameter                                                      | Value       | Units |

|--------|----------------------------------------------------------------|-------------|-------|

| θја    | Thermal Resistance Junction to Ambient <sup>[a][b][c][d]</sup> | 47          | °C/W  |

| Өлс    | Thermal Resistance Junction to Case <sup>[b][c][d]</sup>       | 0.202       | °C/W  |

| Өлв    | Thermal Resistance Junction to Board <sup>[b][c][d]</sup>      | 4.36        | °C/W  |

| TJ     | Operating Junction Temperature <sup>[a][b]</sup>               | -40 to +125 | ٥C    |

| TA     | Operating Ambient Temperature <sup>[a][b]</sup>                | -40 to +85  | ٥C    |

| Тѕтс   | Storage Temperature                                            | -55 to +150 | °C    |

| Твимр  | Maximum Soldering Temperature (Reflow, Pb-Free)                | 260         | ٥C    |

[a] The maximum power dissipation is P<sub>D(MAX)</sub> = (T<sub>J(MAX)</sub> -T<sub>A</sub> / θ<sub>JA</sub> where T<sub>J</sub> is the junction temperature and T<sub>J(MAX)</sub> is 125°C. Exceeding the maximum allowable power dissipation will result in excessive die temperature, and the device will enter thermal shutdown.

[b] This thermal rating was calculated on a JEDEC 51 standard four-layer board with dimensions 3" × 4.5" in still air conditions.

[c] Actual thermal resistance is affected by PCB size, solder joint quality, layer count, copper thickness, airflow, altitude, and other unlisted variables.

[d] For the 40-WLCSP (AZG40) package, connecting the six thermal balls to the internal/external ground planes from the top to bottom sides of the PCB is recommended for improving the overall thermal performance.

#### Table 4.ESD Information

| Test Model                 | Pins      | Ratings | Units |

|----------------------------|-----------|---------|-------|

| Human Body Model (HBM)     | All pins. | ±2000   | V     |

| Charged-Device Model (CDM) | All pins. | ±500    | V     |

## 5. Electrical Characteristics

#### Table 5. Electrical Characteristics

See important notes at the end of the table.  $V_{VRECT} = 5.5V^{[a]}$ ,  $\overline{EN} = 0V$ , and  $C_{OUT} = 10\mu$ F unless otherwise noted.  $T_J = -10^{\circ}$ C to 125°C. Typical values are at 25°C.

| Symbol           | Description                                              | Conditions                                                                                            | Minimum | Typical | Maximum | Units |

|------------------|----------------------------------------------------------|-------------------------------------------------------------------------------------------------------|---------|---------|---------|-------|

|                  |                                                          | VRECT and Under-Voltage Lock-Out                                                                      |         | •       |         |       |

| VRECT            | V <sub>RECT</sub> Operating<br>Voltage <sup>[a][b]</sup> |                                                                                                       | 3.5     | 5.5     | 12.5    | V     |

| VUVLO_RISING     | UVLO Rising                                              | Rising voltage on VRECT pin                                                                           |         | 2.5     | 2.8     | V     |

| VUVLO_FALLING    | UVLO Falling                                             | Falling voltage on VRECT pin                                                                          | 2.1     | 2.3     |         | V     |

| VUVLO_HYS        | UVLO Hysteresis                                          | Falling hysteresis voltage on VRECT pin                                                               | 100     | 200     | 300     | mV    |

|                  |                                                          | <b>Over-Voltage Protection</b>                                                                        |         |         |         |       |

| V <sub>OVP</sub> | Over-Voltage Protection                                  | OVP rising voltage on VRECT pin<br>(default, programmable)                                            | 14      | 15      | 16      | V     |

| VOVP-HYS         | Over-Voltage Hysteresis                                  |                                                                                                       |         | 1       |         | V     |

| Vpre-clamp       | Pre-Clamp Over-Voltage<br>Protection                     | Pre-clamp, rising voltage on the VRECT<br>pin<br>(Default, programmable), VMLDO = 5V                  |         | 12      |         | V     |

| PRE_CLAMP_RNG    | Pre-Clamp Current<br>Range <sup>[c]</sup>                | Programmable                                                                                          | 0       |         | 137     | mA    |

| PRE_CLAMP_STEP   | Step Size                                                |                                                                                                       |         | 7       |         | mA    |

| IPRE_CLAMP       | Set Point                                                | VRECT = 10V, IPRE_CLAMP_SET_POINT = 109mA                                                             |         | 110     |         | mA    |

|                  |                                                          | Quiescent Current                                                                                     |         | •       |         |       |

| IRECT-IDDQ       | I <sub>RECT</sub> Quiescent<br>Current <sup>[c]</sup>    | No external load on VRECT, LDO5P0,<br>and LDO1P8 pins; rectifier not switching;<br>firmware loaded    |         | 8       |         | mA    |

| IRECT-DIS        | IRECT Disable Current                                    | No external load on VRECT, LDO5P0,<br>LDO1P8; /EN = 1.8V; firmware loaded;<br>rectifier not switching |         | 2       |         | mA    |

|                  |                                                          | Main Low-Drop-Out (MLDO) Regulator (V                                                                 | OUT)    |         |         |       |

| IMLDO_LMT_ACC    | Current Limit Accuracy                                   | Current Limit = 0.5A                                                                                  | -3      |         | 3       | %     |

| MLDO_LMT_RNG     | Current Limit Range                                      | Programmable                                                                                          | 0.35    |         | 1.5     | А     |

| IMLDO_LMT_STEP   | Current Limit LSB                                        | Programmable step                                                                                     |         | 50      |         | mA    |

| Vmldo            | Regulated VOUT                                           | Programmable; V <sub>VRECT</sub> = 5.5V ,IOUT = 1A                                                    | 4.8     | 5       | 5.2     | V     |

| VMLDO_STEP       | Output Voltage Step<br>Size <sup>[c]</sup>               |                                                                                                       |         | 25      |         | mV    |

| Vmldo_acc        | Output Voltage<br>Accuracy                               | VOUT = 5V; IOUT = 0.5A                                                                                | -2      |         | 2       | %     |

| Rdson_mldo       | Main LDO                                                 |                                                                                                       |         | 80      |         | mΩ    |

| Symbol                                                                     | Description                                                 | Conditions                                                                     | Minimum   | Typical | Maximum | Units |

|----------------------------------------------------------------------------|-------------------------------------------------------------|--------------------------------------------------------------------------------|-----------|---------|---------|-------|

| V <sub>MLDO_DROP</sub>                                                     | LDO Drop-Out Voltage                                        | IOUT = 0.5A                                                                    |           | 37.5    |         | mV    |

| $V_{\text{MLDO}\_\text{LNR}}$                                              | Line Regulation                                             | VRECT = 5.5V to 8V; IOUT = 100mA                                               | -0.2      |         | 0.2     | %     |

| V <sub>MLDO_PSRR</sub> VOUT Power Supply<br>Rejection Ratio <sup>[c]</sup> |                                                             | VOUT = 5V; IOUT = 0.5 A; 1kHz<br>120mVpp signal summed with VRECT<br>DC level. |           | 80      |         | dB    |

| MLDOLINETRANS                                                              | Line Transient <sup>[c]</sup>                               | VRECT = 5.5V to 8V; IOUT = 100mA,<br>Slew Rate = 1V / 10µs                     |           | 3.5     |         | mV/V  |

| Vmldo_ldr                                                                  | Load Regulation                                             | IOUT = 0 A to 0.5 A; VOUT = 5V                                                 | -0.5      |         | 0.5     | %     |

| MLDOLOADSTEP                                                               | Load Transient Rising <sup>[c]</sup>                        | VOUT = 5V; IOUT = 0 to 500mA,<br>Slew rate = 1A/1µs                            |           | 160     |         | mV/A  |

| tmldo_ss                                                                   | MLDO Start-up Rise<br>Time <sup>[c]</sup>                   | Output capacitance = 10µF; no external<br>load (10% to 90%)                    |           | 150     |         | μs    |

|                                                                            | LC                                                          | 005P0 (For internal use only; LDO5P0 VIN                                       | = VRECT)  |         | 4       |       |

| VLDO5P0                                                                    | LDO5P0 Output                                               | Output capacitance = 1µF, external<br>load=10mA                                | 4.5       | 5       | 5.5     | V     |

| tldo5p0_ss                                                                 | LDO5P0 Start-up Rise<br>Time <sup>[c]</sup>                 | Output capacitance = 1µF; no external<br>load (10% to 90%)                     |           | 160     |         | μs    |

|                                                                            | LD                                                          | O1P8 (For internal use only; LDO1P8 VIN                                        | = LDO5P0) |         |         |       |

| VLDO1P8                                                                    | LDO1P8 Output <sup>[d]</sup>                                | Output capacitance = 1µF, external load<br>= 10mA                              | 1.62      | 1.8     | 1.98    | V     |

| tldo1p8_ss                                                                 | LDO1P8 Start-up Rise<br>Time <sup>[c]</sup>                 | Output capacitance = 1µF; no external load (10% to 90%)                        |           | 7       |         | μs    |

|                                                                            |                                                             | Synchronous Full Bridge Rectifier                                              | ,         |         |         |       |

| Ron_Hs                                                                     | High Side RDS_ON                                            |                                                                                |           | 52      |         | mΩ    |

| Ron_ls                                                                     | Low Side RDS_ON                                             |                                                                                |           | 52      |         | mΩ    |

| Rdson_cma/cmb                                                              | Communication A/B                                           |                                                                                |           | 1       |         | Ω     |

| RDSON_CM1/CM2                                                              | Communication 1/2                                           |                                                                                |           | 1       |         | Ω     |

| VF_RECT                                                                    | Rectifier Body Diode                                        | Forward biased voltage; 100mA                                                  |           | 0.65    |         | V     |

| RECT <sub>FREQ_IN</sub>                                                    | Rectifier Input Operating<br>Frequency Range <sup>[c]</sup> |                                                                                | 100       |         | 300     | kHz   |

|                                                                            |                                                             | Analog-to-Digital Converter                                                    |           |         |         |       |

| Ν                                                                          | Resolution                                                  |                                                                                |           | 12      |         | Bit   |

| <b>f</b> SAMPLE                                                            | Sampling Rate                                               |                                                                                |           | 67.5    |         | kSa/s |

| Channel                                                                    | Number of Channels                                          |                                                                                |           | 8       |         | #     |

| V <sub>IN,FS</sub>                                                         | Full Scale Input<br>Voltage <sup>[e]</sup>                  |                                                                                |           | 2.1     |         | V     |

| Symbol              | Description                                    | Conditions                                                                                    | Minimum         | Typical       | Maximum | Units    |

|---------------------|------------------------------------------------|-----------------------------------------------------------------------------------------------|-----------------|---------------|---------|----------|

|                     |                                                | Thermal Shutdown                                                                              |                 |               |         |          |

| т                   | Thermal Shutdown <sup>[f]</sup>                | Threshold rising                                                                              |                 | 140           |         | °C       |

| T <sub>SD</sub>     |                                                | Threshold falling                                                                             |                 | 120           |         | °C       |

|                     |                                                | Clock                                                                                         |                 |               |         |          |

| fclock_60           | Clock Frequency                                |                                                                                               | 54              | 60            | 66      | MHz      |

|                     | Gen                                            | eral Purpose Push-Pull Inputs/Outputs (GI                                                     | P0, GP1, /EN)   |               |         |          |

| VIH_GP              | Input High Level                               |                                                                                               | 1.4             |               |         | V        |

| VIL_GP              | Input Low Level                                |                                                                                               |                 |               | 0.5     | V        |

| ILKG_GP             | Input Leakage Current                          | 0V and 1.8V                                                                                   | -1              |               | +1      | μA       |

| Voh_gp              | Output Logic High                              | I <sub>OH</sub> = 4mA, 8mA total                                                              | 1.44            |               |         | V        |

| Vol_gp              | Output Logic Low                               | I <sub>OL</sub> = 8mA                                                                         |                 |               | 0.36    | V        |

|                     | SCL, SDA (OD0, O                               | D1) and General Purpose Open Drain Input                                                      | ts/Outputs (OD2 | 2, OD3, /INT) | 1       | <u>.</u> |

| VIH_OD              | Input High Level <sup>[g]</sup>                |                                                                                               | 1.4             |               |         | V        |

| VIL_OD              | Input Low Level <sup>[g]</sup>                 |                                                                                               |                 |               | 0.7     | V        |

| Ilkg_od             | Input Leakage Current                          | V = 0V and 5V (1.8V for /INT)                                                                 | -1              |               | +1      | μA       |

| Vol_od              | Output Logic Low                               | lo∟ = 8mA                                                                                     |                 |               | 0.36    | V        |

|                     |                                                | Ping Detection                                                                                |                 |               |         | <u> </u> |

| VPDET_RC_IH         | Input High Level                               | PDET_RC pin $\geq$ VPDET_RC_IH for PDET_B pin to be pulled-low.                               | 2.2             |               |         | V        |

| Vpdet_rc_il         | Input Low Level                                | PDET_RC pin ≤ VPDET_RC_IL for<br>PDET_B pin to be pulled-high (external<br>pull-up required). |                 |               | 0.5     | V        |

| PDET_RC_LKG         | PDET_RC Leakage                                | V <sub>VRECT</sub> = 0V and V <sub>VRECT</sub> = 5.5V                                         | -1              |               | +1      | μA       |

| VPDETB_OL           | Output Logic Low                               | I <sub>OL</sub> = 1mA                                                                         |                 |               | 0.36    | V        |

|                     |                                                | SCL, SDA (I2C Interface OD0, OD1                                                              | )               |               |         |          |

| fscl                | Clock Frequency                                |                                                                                               |                 |               | 400     | kHz      |

| thd_sta             | Hold Time (Repeated) for START Condition       |                                                                                               | 0.6             |               |         | μs       |

| t <sub>HD_DAT</sub> | Data Hold Time                                 |                                                                                               | 0               |               |         | ns       |

| t <sub>LOW</sub>    | Clock Low Period                               |                                                                                               | 1.3             |               |         | μs       |

| t <sub>ніGH</sub>   | Clock High Period                              |                                                                                               | 0.6             |               |         | μs       |

| tsu_sta             | Set-up Time for<br>Repeated START<br>Condition |                                                                                               | 0.6             |               |         | μs       |

| Symbol              | Description                                          | Conditions            | Minimum | Typical | Maximum | Units |

|---------------------|------------------------------------------------------|-----------------------|---------|---------|---------|-------|

| tвиғ                | Bus Free Time Between<br>STOP and START<br>Condition |                       | 1.3     |         |         | μs    |

| Св                  | Capacitive Load for<br>each Bus Line                 |                       |         | 150     |         | pF    |

| Cı                  | SCL, SDA Input<br>Capacitance                        |                       |         | 5       |         | pF    |

| VIL_I2C             | Input Low Level                                      |                       |         |         | 0.7     | V     |

| VIH_I2C             | Input High Level                                     |                       | 1.4     |         |         | V     |

| Ilkg_12C            | Input Leakage Current                                | V = 0V and 5V         | -1      |         | +1      | μA    |

| V <sub>OL_I2C</sub> | Output Logic Low                                     | I <sub>OL</sub> = 8mA |         |         | 0.36    | V     |

[a] V<sub>RECT</sub> can be as high as 18V but the device "Electrical Characteristics" table limits are not guaranteed under this condition.

[b] Full power transfer might not occur at the minimum VRECT operating specification.

[c] Not 100% production tested. Guaranteed by design.

[d] For internal biasing only; can be used for weak pull-ups or EEPROM power (not to exceed 10mA total).

[e] Any open-drain GPIO (OD2) that is connected to the ADC should remain below 2.1V to prevent saturation of the ADC.

[f] The internal temperature is monitored, and the P9222-R is temporarily deactivated if the temperature exceeds the thermal shutdown limit of 140°C typically. The P9222-R is reactivated when the temperature falls below the thermal shutdown hysteresis (20°C typically).

[g] The pull-up voltage level can be connected to LDO5P0 (5V) or LDO1P8 (1.8V).

## 6. Description of the Wireless Power Charging System

A wireless power charging system has a base station with one or more transmitter coils that make power available via DC-to-AC inverter(s) and transmit the power over a strongly-coupled inductor pair (magnetic induction), or over a loosely-coupled inductor pair (magnetic resonance) to a receiver in a mobile device. A WPC (see Figure 4) uses near-field magnetic induction between coils and can be a free-positioning or magnetically-guided type of system.

In WPC Inductive systems, the amount of power transferred to the mobile device is controlled by the receiver. The receiver sends communication packets to the transmitter to increase power, decrease power, or maintain the power level. The bit rate for the Rx-to-Tx communication link is 2kbps for WPC receivers. It is modulated on top of the power link that exists.

**Base Station** Mobile Device Transmitter Receiver Control Comm Messages Comm Control System -oad Reflected Load DeMod Mod J 3 ٤ Power Conversion Power Pick-up Power

Figure 4. Block Diagram of WPC v1.2.4-Compliant Wireless Power Transfer System

Note: For the more current information, see the WPC Specification at http://www.wirelesspowerconsortium.com/.

## 7. Typical Performance Characteristics

The following performance characteristics were taken using a P9235-RB-EVK, with WPC A11a coil and P9222-R EVK with MQQRR303008S8R2 coil with default configuration in at  $T_A = 25^{\circ}$ C unless otherwise noted.

### Figure 5. System Efficiency vs Output Current

Figure 6. VRECT vs IOUT, Vout = 5.0V

#### Figure 8. PDIFF (PTX-PRX) vs lout on NOK9 Transmitter

#### Figure 9. Initial Startup

Figure 11. Load Transient Response 1 (Vout = 5V, lout 0mA to 500mA)

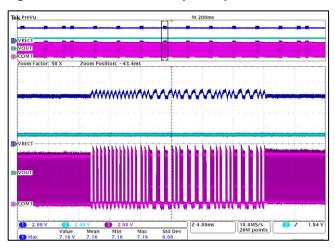

Figure 13. Ping Detect Timing

#### Figure 10. Active Charging Area (Efficiency, 14 × 15 mm)

Figure 12. Load Transient Response 2 (Vout = 5V, lout 0mA to 1000mA)

Figure 14. AC Modulation (COM1)

## 8. Theory of Operation

The P9222-R is a highly-integrated wireless power receiver for mobile or stationary devices. The device can receive and provide up to 5W to its output when powered wirelessly using near-field magnetic induction. The device is optimized for efficient power transfer in low-power wearable applications.

## 8.1 Overview

The simplified internal block diagram of the P9222-R is shown in Figure 2. Energy is transferred wirelessly from the transmitter to the P9222-R via an external Rx coil and  $C_S$  capacitor(s). The external LC is connected to the AC1 and AC2 pins to be full-wave-rectified (AC-to-DC).

#### 8.1.1 Low-Power Ping Detection

Once charging has completed, the wireless power connection to the Tx can be programmed to terminate to save power. In order to inform the system that the P9222-R is still on the charger, the PDETB pin will be held LOW as long as Tx ping pulses are detected. The resistor and capacitor (RC) connected to the PDET\_RC pin should be selected such that the time constant of the RC maintains an adequate charge between Tx ping events to prevent PDETB from changing states until the device is removed from the Tx. The values of the RC circuit should be selected based on the expected ping time interval of the Tx. For more information, see "Low-Power Ping Detection Operation".

#### 8.1.2 Rx Operation

The wireless power is stored on a capacitor(s) connected to the VRECT pin in Rx mode. Until the voltage across the VRECT capacitor exceeds the under-voltage lock-out (UVLO) threshold, the rectification is performed by the body diodes of the synchronous full bridge rectifier FETs. After the internal biasing circuit is enabled, the driver and control blocks operate the MOSFET switches of the rectifier in various modes to maintain reliable connections and optimal efficiency. An internal ADC monitors the voltage at VRECT and the load current. The P9222-R sends instructions to the wireless power transmitter to increase or decrease the amount of power transferred or to terminate power transmission based on these readings. The LDO VOUT pin can be pre-programmed from 3.5V up to 12V or changed after startup using I<sup>2</sup>C commands. The headroom and target VRECT value will automatically adjust based on the latest VOUT set-point programmed value. The internal temperature is continuously monitored to ensure proper operation.

## 8.2 Wireless Power Control

The voltage at VRECT and the current through the rectifier are sampled periodically and digitized by the ADC. The digital equivalents of the voltage and current are supplied to the internal control logic, which decides whether the loading conditions on VRECT indicate that a change in the operating point is required. If the load is heavy enough to bring the voltage at VRECT below its target, the transmitter is instructed to move its frequency lower, closer to resonance. If the voltage at VRECT is higher than its target, the transmitter is instructed to increase its frequency. To maximize efficiency, the voltage at VRECT is programmed to decrease as the LDO's load current increases.

## 8.3 Startup

When a mobile device containing the P9222-R is placed on a WPC "Qi" charging pad, it responds to the transmitter's "ping" signal by rectifying the AC power from the transmitter and storing it on a capacitor connected to VRECT. During the "ping" phase, once the rectifier provides a voltage at the VRECT pin above the UVLO threshold, the digital section of the P9222-R enables communication. The control loop of the P9222-R adjusts the rectifier voltage by sending Control Error Packets (CEPs) to the transmitter before and after it enables the VOUT LDO.

The VOUT LDO is enabled when the power transfer phase is initiated and the voltage at VRECT (i.e., the output of the full-wave synchronous rectifier reaches the target voltage that includes headroom in addition to the LDO VOUT target voltage). For example, if the VOUT voltage target is 5V, the target VRECT voltage is VOUT plus headroom. If the VRECT target voltage is not reached within 1 second after entering the power transfer phase, the VOUT LDO will be enabled automatically.

### 8.4 **Power Transfer**

Once the "identification and configuration" phase is completed then the transmitter initiates the power transfer mode. The P9222-R control circuit measures the rectifier voltage, sends CEPs to the transmitter to adjust the rectifier voltage to the level required to maximize the efficiency of the linear regulator, and sends Received Power Packets (RPPs) to notify the Tx of the current for foreign object detection (FOD) to guarantee safe, efficient power transfer. For more information about WPC-compliant power transfer, see "WPC-Compliant Power Transfer."

### 8.5 Synchronous Rectifier

The efficiency of the full-bridge rectifier in the P9222-R is increased by operating in full synchronous rectifier mode. The rectifier is comprised of four self-driven switches that work in a full synchronous mode of operation when the load is higher than a programmable level (typically 150mA for BPP operation). Below that threshold, the rectifier works in half-synchronous rectification mode. At power-up, when the voltage is below the UVLO threshold, the rectifier functions by using the body diodes associated with the NMOS transistors. The BST capacitors are used to provide power to drive the gates of the high-side NMOS switches.

## 8.6 Over-Voltage Protection

In the event that the input voltage increases above 15V (default setting), the Rx sends control error packets to the transmitter in an attempt to bring the rectifier voltage back to a safe operating voltage level while simultaneously clamping the incoming energy using the internal high voltage OVP FET for VRECT over-voltage clamping control. The clamp is released when the VRECT voltage falls below the V<sub>OVP</sub> hysteresis falling level. The P9222-R also sends interrupts to the application processor (AP) when the over-voltage event occurs.

### 8.7 Over-Current Protection and Thermal Shutdown

The P9222-R uses over-current and thermal protection by sending an interrupt to the AP to notify the host controller if the output current or die temperature has exceeded the operating limits. In the event that an overcurrent condition exists, the interrupt is sent to the AP with the expectation that it will respond by reducing the output consumption being drawn from the P9222-R. If the overcurrent condition persists and is not corrected, then P9222-R die temperature increases can be expected. In the event that the die temperature exceeds the thermal shutdown level, an End Power Transfer packet is sent to the transmitter to terminate power transfer and protect the P9222-R from thermal stress. The current limit level is programmable. The P9222-R sends interrupts to the AP if the current limit is reached or the die temperature reaches elevated levels to allow the AP an opportunity to reduce the load current in order to prevent power transfer interruptions.

## 8.8 External Temperature Sensing

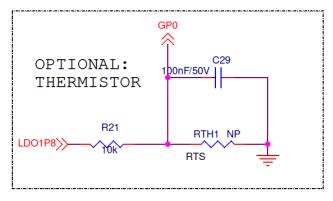

The P9222-R includes an optional temperature sense input pin on GP0. It is used to monitor a remote temperature, such as on an Rx coil or a PC board using an external thermistor circuit shown in Figure 15.

The GP0 pin voltage can be calculated using the following equation,

$$V_GP0 = V_LD01P8 \times \frac{NTC}{R21+NTC}$$

#### **Equation 1**

where NTC is the thermistor's resistance (RTH1) and R21 is the pull-up resistor connected to the 1.8V (LDO1P8) supply voltage on the P9222-R Evaluation Board. The over-temperature interrupt is triggered if the voltage on the GP0 pin is lower than 0.6V. The RTH1 is not populated on the P9222-R Evaluation Board.

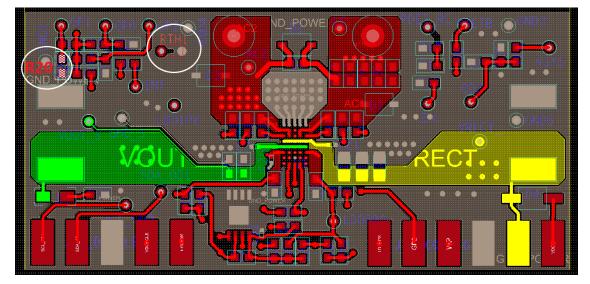

#### Figure 15. RTH1 and R21 Schematic Location

Figure 16. RTH1 and R21 PCB Location

## 8.9 Rectifier and VRECT Level

Once VRECT powers up to greater than UVLO, the full-bridge rectifier switches to half synchronous or full synchronous mode (depending on the loading conditions) to efficiently transfer energy from the transmitter to the load applied to VOUT. The VRECT pin must not be directly loaded. The rectified voltage will automatically self-adjust based on the programmed output setting to regulate throughout for all phases of charging to maintain adequate headroom that is balanced with optimal efficiency.

## 8.10 Interrupt Output

In Wireless Power RX mode, the /INT pin can be programmed to go LOW to indicate that an over-current, over-voltage, or over-temperature event has occurred. This feature is programmable and can be implemented using the /INT.

## 8.11 Low Drop-Out (LDO) Regulators

The P9222-R has three LDO regulators. The primary VOUT LDO is powered by VRECT. The VOUT LDO can be programmed to any voltage between 3.5V and 10V; however, the output voltage setting should be compatible with the wireless Tx capability and coil type. The LDO5P0 is powered directly from VRECT, and LDO1P8 is powered from LDO5P0. Both are used for supplying power to internal low-voltage blocks. The LDOs must have local ceramic bypass capacitors placed near the P9222-R. For recommended values, follow the application schematic in Figure 32.

## 8.12 MLDO Output Enable Conditions

After the P9222-R is energized wirelessly by a valid Tx and reaches the power transfer state, there are two criteria that must be met prior to the VOUT MLDO regulator being automatically enabled after start-up. Upon connection to a Tx, the P9222-R sends CEP +55 in order to drive VRECT up to 6.5V and also starts a 1-second timer to allow VRECT to reach the target. After this timer expires, one of two conditions must be met before the VOUT output is enabled: CEP values are less than +4 (indicates VRECT has reached the target), or 5 seconds pass. Either of these events will trigger the P9222-R to enable VOUT. In cases where VRECT is still below the target voltage (5 seconds pass and VRECT < Vrect\_Target), VOUT is enabled in order to allow charging to start. When VRECT is below Vrect\_Target, full power charging may not be possible because the Tx is not providing adequate energy for full power to be transferred.

## 8.13 Output Power Options

The P9222-R supports configurations such as described in the WPC v1.2.4 Baseline Power Profile (BPP) specification. The P9222-R can be programmed to optimize power delivery for low-power wearable applications and can also provide VOUT and VRECT battery voltage tracking to reduce losses, further improving efficiency and reducing heat generation during charging.

## 9. WPC Mode Characteristics

For a description of the startup process for wireless charging, which is compliant with the WPC protocol, see "Startup".

### 9.1 WPC-Compliant Power Transfer

Once the "identification and configuration" phase is completed, the transmitter initiates the power transfer phase. The P9222-R control circuit measures the rectifier voltage and sends CEPs to the transmitter to adjust the rectifier voltage to the level required to maximize the efficiency of the linear regulator and to notify the Tx of the current Received Power Packet for foreign object detection (FOD) in order to guarantee safe, efficient power transfer. The P9222-R is compatible with WPC (v1.2.4) and can use compatible Rx coils. Each receiver coil type has a unique inductance value. As such, a unique resonant capacitor ( $C_S$ ) is used for a given type of receiver coil.

## 9.2 Advanced Foreign-Object Detection (FOD) in WPC Mode

When metallic objects are exposed to an alternating magnetic field, eddy currents cause such objects to heat up. Examples of parasitic metal objects are coins, keys, paperclips, etc. The amount of heating depends on the amplitude and frequency of the magnetic field coupled, as well as the characteristics of the object, such as its resistivity, size, and shape. In a wireless power transfer system, the heating manifests itself as a power loss, and therefore a reduced power transfer efficiency. Moreover, if no appropriate measures are taken, the heating could lead to unsafe situations if the objects reach high temperatures.

WPC power transmitters and receivers need to also compensate for the power loss due to parasitic metals intentionally designed into the final product; i.e., metals that are neither part of the power transmitter nor of the power receiver, but which absorb power from magnetic field coupling during the power transfer, such as Li-ion batteries, metallic cases, etc.

The P9222-R uses advanced FOD techniques to detect foreign objects placed on or near the transmitter base station. The FOD algorithm includes values that are programmable through either the I2C interface or external EEPROM memory bits. Programmability is necessary so that the FOD settings can be optimized to match the power transfer characteristics of each particular WPC system to include the power losses of the Tx and Rx coils, battery, shielding, and case materials under no load to full load conditions. The values are based on the comparison of the received power against a reference power curve so that any foreign object can be sensed when the received power is different from the expected system power.

The P9222-R FOD values need to be tuned prior to production for WPC compliance using final production hardware and coils.

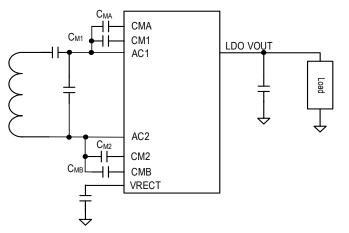

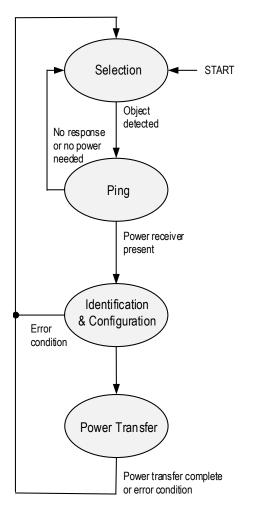

### 9.3 WPC Modulation/Communication

The P9222-R operates in the WPC mode using a single LC tank Rx coil and requires AC modulation capacitor connections for WPC communication. The capacitors  $C_{M1}$  and  $C_{M2}$  (connected to pins CM1 and CM2 respectively; see Figure 17) and the LC tank accomplish WPC modulation. The capacitor values should be tuned to achieve maximum efficiency while still providing adequate communications.

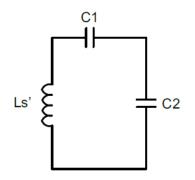

#### Figure 17. Rx Modulation Components