# **High-Speed CAN Transceiver With Standby Mode**

## 1. Description

The TJA1042 high-speed CAN transceiver provides an interface between a Controller Area Network (CAN) protocol controller and the physical two-wire CAN bus. The transceiver is designed for high-speed CAN applications in the automotive industry, providing the differential transmit and receive capability to (a microcontroller with) a CAN protocol controller.

#### Table 1. Quick Reference Data

| PARAMETER                         | SYMBOL             | CONDITION               | MIN. | MAX. | UNIT  |

|-----------------------------------|--------------------|-------------------------|------|------|-------|

| Supply voltage                    | Vcc                |                         | 4.5  | 5.5  | V     |

| Maximum transmission rate         | 1/t <sub>bit</sub> | Non-return to zero code | 5    |      | Mbaud |

| CANH/CANL input or output voltage | V <sub>can</sub>   |                         | -70  | +70  | V     |

| Bus differential voltage          | $V_{\text{diff}}$  |                         | 1.5  | 3.0  | V     |

| Virtual junction temperature      | T <sub>vj</sub>    |                         | -40  | 150  | °C    |

### 2. Features

- Fully compatible with the ISO 11898 standard

- Thermally protected

- Transmit Data (TXD) dominant time-out function

- Very low-current Standby mode with host and bus wake-up capability

- $V_{\rm IO}$  input on TJA1042T/3 and TJA1042TK/3 allows for direct interfacing with 3 V to 5 V

microcontrollers

- Transmit Data (TXD) dominant time-out function

- High voltage robustness on CAN pins (±70 V)

- Timing guaranteed for data rates up to 5 Mbit/s in the CAN FD fast phase

- Undervoltage detection on pins  $V_{\text{CC}}$  and  $V_{\text{IO}}$

- Bus-dominant time-out function in Standby mode

## 3. Ordering Information

| Type Number | Package Type    | Packing     | Notes |

|-------------|-----------------|-------------|-------|

| TJA1042T    | SOIC-8          | Tape & Reel |       |

| TJA1042T/3  | SOIC-8          | Tape & Reel |       |

| TJA1042TK/3 | DFN3*3-8/HVSON8 | Tape & Reel |       |

Note: If the physical information is inconsistent with the ordering information, please refer to the actual product.

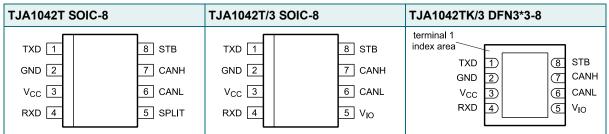

## 4. Pin Configuration

# 5. Pin Description

| Symbol          | Pin              | Description                                                                       |

|-----------------|------------------|-----------------------------------------------------------------------------------|

| TXD             | 1                | transmit data input                                                               |

| GND             | 2 <sup>[1]</sup> | ground supply                                                                     |

| V <sub>cc</sub> | 3                | supply voltage                                                                    |

| RXD             | 4                | receive data output; reads out data from the bus lines                            |

| SPLIT           | 5                | common-mode stabilization output; in TJA1042T version only                        |

| V <sub>IO</sub> | 5                | supply voltage for I/O level adapter; in TJA1042T/3 and TJA1042TK/3 versions only |

| CANL            | 6                | LOW-level CAN bus line                                                            |

| CANH            | 7                | HIGH-level CAN bus line                                                           |

| STB             | 8                | Standby mode control input                                                        |

[1]: HVSON8 package die supply ground is connected to both the GND pin and the exposed center pad. The GND pin must be soldered to board ground. For enhanced thermal and electrical performance, it is recommended that the exposed center pad also be soldered to board ground.

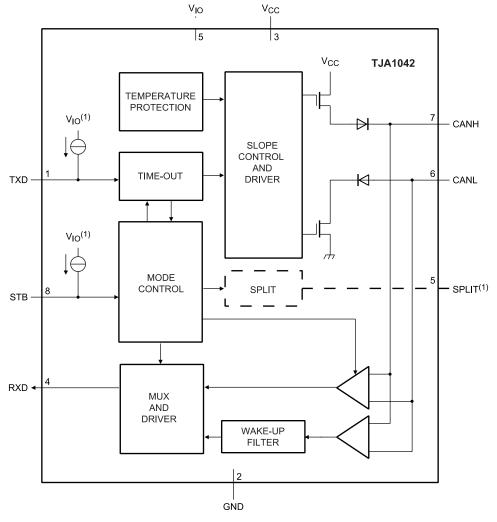

## 6. Functional Block Diagram

(1) In a transceiver with a SPLIT pin, the  $V_{\rm IO}$  input is internally connected to  $V_{\rm CC}.$

# 7. Limiting Values

| PARAMETER                                      | SYMBOL                         | VALUE     | UNIT |

|------------------------------------------------|--------------------------------|-----------|------|

| Supply voltage                                 | V <sub>CC</sub>                | -0.3~+7   | V    |

| Voltage on MCU pins                            | TXD, RXD, STB, V <sub>IO</sub> | -0.3~+7   | V    |

| Voltage range at any bus terminal (CANH, CANL) | CANL, CANH                     | -70~70    | V    |

| Voltage between pin CANH and pin CANL          | Vcanh-canl                     | -27~27    | V    |

| Transient voltage on pins CANH, CANL and SPLIT | V <sub>tr</sub>                | -200~+200 | V    |

| Storage temperature                            |                                | -55~150   | °C   |

| Virtual junction temperature                   | T <sub>vj</sub>                | -40~150   | °C   |

| Welding temperature range                      |                                | 300       | °C   |

The maximum limit parameters means that exceeding these values may cause irreversible damage to the device. Under these conditions, it is not conducive to the normal opration of the device. The continuous operation of the device at the maximum allowable rating may affect the reliability of the device. The reference point for all voltages is ground.

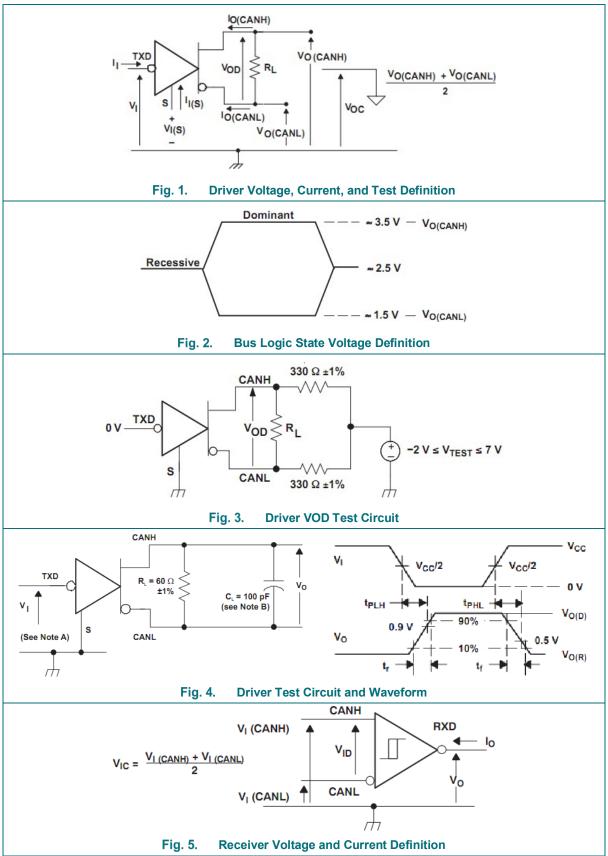

## 8. Driver Electrical Characteristics

| PARAMETER                                                                                                                  | SYMBOL                   | CONDITION                                                                          | MIN.               | TYP.               | MAX.               | UNIT |

|----------------------------------------------------------------------------------------------------------------------------|--------------------------|------------------------------------------------------------------------------------|--------------------|--------------------|--------------------|------|

| CANH dominant output voltage                                                                                               | V <sub>OH(D)</sub>       | V <sub>I</sub> =0V, STB=0V, R <sub>L</sub> =60Ω,                                   | 2.9                | 3.4                | 4.5                | V    |

| CANL dominant output voltage                                                                                               | V <sub>OL(D)</sub>       | Fig.1, Fig.2                                                                       | 0.8                |                    | 1.5                | V    |

|                                                                                                                            | V                        | V <sub>I</sub> =3V, STB=0V, R <sub>L</sub> =60Ω,                                   | 2                  | 0.5V <sub>cc</sub> | 2                  | v    |

| Bus recessive output voltage                                                                                               | V <sub>O(R)</sub>        | Fig.1, Fig.2                                                                       | 2                  | 0.3000             | 3                  | v    |

| Bus dominant differential output                                                                                           | V                        | $V_I=0V$ , STB=0V, $R_L=60\Omega$ ,                                                | 1.5                |                    | 3                  | v    |

| voltage                                                                                                                    | $V_{OD(D)}$              | Fig.1, Fig.2                                                                       | 1.5                |                    | 3                  | v    |

| Bus recessive differential output                                                                                          | V                        | V <sub>I</sub> =3V, S=0V, Fig.1, Fig.2                                             | -0.012             |                    | 0.012              | V    |

| voltage                                                                                                                    | V <sub>OD(R)</sub>       | VI=3V, STB=0V, NO LOAD                                                             | -0.5               |                    | 0.05               | V    |

| Transmitter dominant voltage                                                                                               | V                        |                                                                                    | -400               |                    | 400                | mV   |

| symmetry                                                                                                                   | V <sub>dom(TX)</sub> sym | $V_{dom(TX)sym} = V_{CC} - V_{CANH} - V_{CANL}$                                    | -400               |                    | 400                | IIIV |

| Transmitter voltage symmetry                                                                                               | V <sub>TXsym</sub>       | $V_{TXsym} = V_{CANH} + V_{CANL}$                                                  | 0.9V <sub>CC</sub> |                    | 1.1V <sub>cc</sub> | V    |

| Common-mode output voltage                                                                                                 | Voc                      | STB=0V, Fig.8                                                                      | 2                  | $0.5V_{\text{CC}}$ | 3                  | V    |

| Peak-to-peak                                                                                                               | ΔV <sub>OC</sub>         |                                                                                    |                    | 30                 |                    | mV   |

| Common-mode output voltage                                                                                                 | AVOC                     |                                                                                    |                    | 30                 |                    | IIIV |

|                                                                                                                            |                          | CANH=-12V, CANL=open, Fig.11                                                       | -105               | -72                |                    | mA   |

| vymmetry V<br>Fransmitter voltage symmetry V<br>Common-mode output voltage V<br>Peak-to-peak<br>Common-mode output voltage | 1                        | CANH=12V, CANL=open, Fig.11                                                        |                    | 0.36               | 1                  | mA   |

| Short-circuit output current                                                                                               | l <sub>os</sub>          | CANL=-12V, CANH=open, Fig.11                                                       | -1                 | 0.5                |                    | mA   |

|                                                                                                                            |                          | CANL=12V, CANH=open, Fig.11                                                        |                    | 71                 | 105                | mA   |

|                                                                                                                            | 1                        | -27V <canh<32v< td=""><td>2.0</td><td></td><td>о<i>г</i></td><td></td></canh<32v<> | 2.0                |                    | о <i>г</i>         |      |

| Recessive output current                                                                                                   | I <sub>O(R)</sub>        | 0 <v<sub>CC&lt;5.25V</v<sub>                                                       | -2.0               |                    | 2.5                | mA   |

(Typical in V<sub>CC</sub>=+5V, V<sub>IO</sub>=5V, R<sub>L</sub>=60 $\Omega$  and T<sub>emp</sub>=25°C unless specified otherwise)

# 9. Driver Switching Characteristics

| PARAMETER                                        | SYMBOL               | CONDITION     | MIN. | TYP. | MAX. | UNIT |

|--------------------------------------------------|----------------------|---------------|------|------|------|------|

| Propagation delay time, low-to-high-level output | t <sub>PLH</sub>     | STB=0V, Fig.4 |      | 90   |      | ns   |

| Propagation delay time, low-to-high-level output | t <sub>PHL</sub>     |               |      | 65   |      | ns   |

| Differential output signal rise time             | t <sub>r</sub>       |               |      | 45   |      | ns   |

| Differential output signal fall time             | t <sub>f</sub>       |               |      | 45   |      | ns   |

| Enable time from standby mode to dominant        | t <sub>EN</sub>      | Fig.7         |      | 10   | 45   | μs   |

| TXD dominant time-out time                       | t <sub>dom_TXD</sub> | Fig 10        | 0.8  | 2    | 4    | ms   |

| Bus dominant time-out time                       | t <sub>dom_BUS</sub> |               | 0.8  | 2    | 4    | ms   |

| Bus wake-up filter time                          | t <sub>WAKE</sub>    |               | 0.5  |      | 5    | μs   |

(Typical in V<sub>CC</sub>=+5V, V<sub>IO</sub>=5V, R<sub>L</sub>=60 $\Omega$  and T<sub>emp</sub>=25°C unless specified otherwise)

## **10. Receiver Electrical Characteristics**

| PARAMETER                                                 | SYMBOL                | CONDITION                    | MIN. | TYP. | MAX. | UNIT |

|-----------------------------------------------------------|-----------------------|------------------------------|------|------|------|------|

| Positive-going input threshold voltage                    | V <sub>IT+</sub>      | STB=0V, Fig.5                |      |      | 900  | mV   |

| Negative-going input threshold voltage                    | V <sub>IT-</sub>      |                              | 500  |      |      | mV   |

| Hysteresis voltage (V <sub>IT+</sub> – V <sub>IT–</sub> ) | V <sub>HYS</sub>      |                              | 50   | 120  | 200  | mV   |

| Positive-standby input threshold voltage                  | V <sub>IT+(STB)</sub> | Standby mode                 |      |      | 1150 | mV   |

| Negative-standby input threshold voltage                  | V <sub>IT-(STB)</sub> | Standby mode                 | 400  |      |      | mV   |

|                                                           |                       | CANH or                      |      |      |      |      |

| Power-off bus input current                               | $I_{(OFF)}$           | CANL=5V,                     | -5   |      | 5    | μA   |

|                                                           |                       | Other pin=0V                 |      |      |      |      |

| Input capacitance to ground, (CANH or CANL)               | Cı                    |                              |      | 24   |      | pF   |

| Differential input capacitance                            | CID                   |                              |      | 12   |      | pF   |

| Input resistance,(CANH or CANL)                           | R <sub>IN</sub>       |                              | 9    | 15   | 28   | kΩ   |

| Differential input resistance                             | R <sub>ID</sub>       | TXD=V <sub>IO</sub> , STB=0V | 19   | 30   | 52   | kΩ   |

| Input resistance matching                                 | R <sub>Imatch</sub>   | CANH=CANL                    | -2%  |      | 2%   |      |

| The range of common-mode voltage                          | V <sub>сом</sub>      |                              | -30  |      | 30   | V    |

(Typical in V<sub>CC</sub>=+5V, V<sub>IO</sub>=5V, R<sub>L</sub>=60 $\Omega$  and T<sub>emp</sub>=25°C unless specified otherwise)

## **11. Receiver Switching Characteristics**

| PARAMETER                                        | SYMBOL           | CONDITION                  | MIN. | TYP. | MAX. | UNIT |

|--------------------------------------------------|------------------|----------------------------|------|------|------|------|

| Propagation delay time, low-to-high-level output | t <sub>PLH</sub> | STB=0V or $V_{CC}$ , Fig.6 |      | 65   |      | ns   |

| Propagation delay time, low-to-high-level output | t <sub>PHL</sub> |                            |      | 60   |      | ns   |

| RXD signal rise time                             | t <sub>r</sub>   |                            |      | 10   |      | ns   |

| RXD signal fall time                             | t <sub>f</sub>   |                            |      | 10   |      | ns   |

(Typical in V\_{CC}=+5V, V\_{IO}=5V, R\_L=60\Omega and  $T_{emp}{=}25^\circ C$  unless specified otherwise)

# **12. Device Switching Characteristics**

| PARAMETER                                               | SYMBOL                | CONDITION                    | MIN. | TYP. | MAX. | UNIT |

|---------------------------------------------------------|-----------------------|------------------------------|------|------|------|------|

| Loop delay1, driver input to receiver output, Recessive | -                     | STB=0V,                      |      | 90   | 220  | 20   |

| to Dominant                                             | T <sub>d(LOOP1)</sub> | Fig.9                        |      | 90   | 220  | ns   |

| Loop delay 2, driver input to receiver output, Dominant | -                     |                              |      | 100  | 220  | 20   |

| to Recessive                                            | T <sub>d(LOOP2)</sub> | l d(LOOP2)                   |      | 100  | 220  | ns   |

| Bit time on Bus                                         | +                     | t <sub>bit(TXD)</sub> =500ns | 435  |      | 530  | ns   |

|                                                         | t <sub>bit(BUS)</sub> | t <sub>bit(TXD)</sub> =200ns | 155  |      | 210  | ns   |

|                                                         |                       | t <sub>bit(TXD)</sub> =500ns | 400  |      | 550  | ns   |

| Bit time on pin RXD                                     | t <sub>bit(RXD)</sub> | t <sub>bit(TXD)</sub> =200ns | 120  |      | 220  | ns   |

(Typical in V<sub>CC</sub>=+5V, V<sub>IO</sub>=5V, R<sub>L</sub>=60 $\Omega$  and T<sub>emp</sub>=25°C unless specified otherwise)

## **13. Over Temperature Protection**

| PARAMETER                     | SYMBOL      | CONDITION | MIN. | TYP. | MAX. | UNIT |

|-------------------------------|-------------|-----------|------|------|------|------|

| Shutdown junction temperature | $T_{j(sd)}$ |           |      | 190  |      | °C   |

(Typical in V\_{CC}=+5V, V\_{IO}=5V, R\_L=60\Omega and  $T_{emp}{=}25^\circ C$  unless specified otherwise)

## 14. Undervoltege Detection

| PARAMETER                                             | SYMBOL         | CONDITION | MIN. | TYP. | MAX. | UNIT |

|-------------------------------------------------------|----------------|-----------|------|------|------|------|

| undervoltage detection voltage on pin $V_{\text{CC}}$ | $V_{uvd\_VCC}$ |           | 3.5  |      | 4.5  | V    |

| undervoltage detection voltage on pin $V_{\text{IO}}$ | $V_{uvd\_VIO}$ |           | 1.5  |      | 2.5  | V    |

(Typical in V\_{CC}=+5V, V\_{IO}=5V, R\_L=60\Omega and  $T_{emp}{=}25^\circ C$  unless specified otherwise)

## **15. TXD-Pin Characteristics**

| PARAMETER                             | SYMBOL               | CONDITION                                                 | MIN.                     | TYP. | MAX.                              | UNIT  |

|---------------------------------------|----------------------|-----------------------------------------------------------|--------------------------|------|-----------------------------------|-------|

| HIGH-level input current              | I <sub>IH(TXD)</sub> | TXD=V <sub>IO</sub>                                       | -5                       |      | 5                                 | μA    |

| LOW-level input current               | I <sub>IL(TXD)</sub> | TXD=0V                                                    | -260                     | -150 | -30                               | μA    |

| When $V_{CC}$ =0V, current on TXD pin | I <sub>O(OFF)</sub>  | V <sub>CC</sub> =V <sub>IO</sub> =0V, TXD=V <sub>IO</sub> | -1                       |      | 1                                 | μA    |

| HIGH-level input voltage              | VIH                  |                                                           | $0.7V_{10}$ <sup>①</sup> |      | V <sub>IO</sub> <sup>①</sup> +0.3 | V     |

| LOW-level input voltage               | VIL                  |                                                           | -0.3                     |      | 0.3V <sub>I0</sub> ®              | V     |

| Open voltage on TXD pin               | T <sub>XDO</sub>     |                                                           | Н                        |      |                                   | logic |

(Typical in V\_{CC}=+5V, V\_{IO}=5V, R\_L=60\Omega and  $T_{emp}{=}25^\circ C$  unless specified otherwise)

### **16. STB Pin Characteristics**

| PARAMETER                            | SYMBOL               | CONDITION                                                 | MIN.                  | TYP. | MAX.                              | UNIT |

|--------------------------------------|----------------------|-----------------------------------------------------------|-----------------------|------|-----------------------------------|------|

| HIGH-level input current on STB Pin  | I <sub>IH(STB)</sub> | STB=V <sub>IO</sub>                                       | -2                    |      | 2                                 | μA   |

| LOW-level input current on STB Pin   | I <sub>IL(STB)</sub> | STB=0V                                                    | -20                   |      | -2                                | μA   |

| V <sub>CC</sub> =0V, STB Pin current | I <sub>O</sub> (off) | V <sub>CC</sub> =V <sub>IO</sub> =0V, STB=V <sub>IO</sub> | -1                    |      | 1                                 | μA   |

| HIGH-level input voltage             | VIH                  |                                                           | 0.7 V <sub>IO</sub> ® |      | V <sub>IO</sub> <sup>①</sup> +0.3 | V    |

| LOW-level input voltage              | VIL                  |                                                           | -0.3                  |      | 0.3V <sub>I0</sub> ®              | V    |

| Open voltage on STB Pin              | STB <sub>0</sub>     |                                                           | Н                     |      | logic                             |      |

$(TJA1042T, V_{IO}=V_{CC} (Typical in V_{CC}=+5V, V_{IO}=5V, R_L=60\Omega \text{ and } T_{emp}=25^{\circ}C \text{ unless specified otherwise})$

# **17. RXD Pin Characteristics**

| PARAMETER                             | SYMBOL               | CONDITION                                                 | MIN. | TYP. | MAX. | UNIT |

|---------------------------------------|----------------------|-----------------------------------------------------------|------|------|------|------|

| HIGH-level input current              | I <sub>OH(RXD)</sub> | $V_{IO}=V_{CC}$ , RXD= $V_{IO}$ -0.4V                     | -8   | -3   | -1   | mA   |

| LOW-level input current               | I <sub>OL(RXD)</sub> | RXD=0.4V, BUS dominat                                     | 2    | 5    | 12   | mA   |

| When $V_{CC}$ =0V, current on STB pin | I <sub>O(off)</sub>  | V <sub>CC</sub> =V <sub>IO</sub> =0V, RXD=V <sub>IO</sub> | -1   |      | 1    | μA   |

(Typical in V<sub>CC</sub>=+5V, V<sub>IO</sub>=5V, R<sub>L</sub>=60 $\Omega$  and T<sub>emp</sub>=25°C unless specified otherwise)

## **18. Common Mode Stabilization Output**

| PARAMETER                | SYMBOL             | CONDITION                        | MIN.               | TYP.         | MAX.               | UNIT |

|--------------------------|--------------------|----------------------------------|--------------------|--------------|--------------------|------|

| SPLIT Pin output voltage | V <sub>SPLIT</sub> | -500μΑ<Ι <sub>SPLIT</sub> <500μΑ | 0.3V <sub>CC</sub> | $0.5 V_{CC}$ | 0.7V <sub>CC</sub> | V    |

(Typical in V\_{CC}=+5V, V\_{IO}=5V, R\_L=60\Omega and  $T_{emp}{=}25^\circ C$  unless specified otherwise)

## **19. Supply Current**

| PARAMETER              |                       | SYMBOL              | CONDITION                                   | MIN. | TYP. | MAX.        | UNIT     |

|------------------------|-----------------------|---------------------|---------------------------------------------|------|------|-------------|----------|

|                        | Common Mode Dominant  | I <sub>CC_D</sub>   | Bus dominant                                |      | 45   | 70          | mA       |

|                        | Common Mode Recessive | I <sub>CC_R</sub>   | Bus recessive                               |      | 5    | 10          | mA       |

| Supply current         |                       |                     | STB=V <sub>CC</sub> , TXD=V <sub>IO,</sub>  |      | 0.5  | 5           |          |

| on Pin $V_{\text{CC}}$ | Standby Mode          |                     | (TJA1042T/3)                                |      | 0.5  | 5           | μA       |

|                        |                       | I <sub>CC_STB</sub> | STB=V <sub>CC</sub> , TXD=V <sub>CC</sub> , |      | 12   | 25          |          |

|                        |                       |                     | (TJA1042T)                                  |      | 12   | 20          | μA       |

|                        | Common Mode Dominant  |                     | RXD open, STB=0V,                           |      | 350  | 1000<br>200 | μA<br>μA |

| Supply ourrent         | Common wode Dominant  | I <sub>IO_D</sub>   | TXD=0V                                      |      | 350  |             |          |

| Supply current         | Common Mode recessive |                     | RXD open, STB=0V,                           |      | 80   |             |          |

| on Pin V <sub>IO</sub> | Common wode recessive | I <sub>IO_R</sub>   | TXD=V <sub>IO</sub>                         |      |      |             |          |

|                        | Standby Mode          | I <sub>IO_STB</sub> | STB=TXD=V <sub>IO</sub>                     |      | 10   | 20          | μA       |

(Typical in V\_{CC}=+5V, V\_{IO}=5V, R\_L=60\Omega and  $T_{emp}{=}25^\circ C$  unless specified otherwise)

### **20. ESD Characteristics**

| PARAMETER                  | SYMBOL                        | CONDITION                      | MIN. | TYP. | MAX. | UNIT |

|----------------------------|-------------------------------|--------------------------------|------|------|------|------|

|                            | V                             | IEC 61000-4-2:                 | 4    |      | . 4  |      |

| At any other pin (IEC)     | V <sub>ESD_IEC</sub>          | Contact Discharge (CANH, CANL) | -4   |      | +4   | kV   |

| Human Body Model (HBM)     | $V_{\text{ESD}_{\text{HBM}}}$ |                                | -8   |      | +8   | kV   |

| Charged Device Model (CDM) | V <sub>CDM</sub>              |                                | -750 |      | +750 | V    |

| Machine Model (MM)         | V <sub>MM</sub>               |                                | -300 |      | +300 | V    |

# 21. Function Table

#### Table 2. CAN Transceiver Truth Table

| <b>TXD</b> <sup>(1)</sup> | STB <sup>(1)</sup> | CANH <sup>(1)</sup> | CANL <sup>(1)</sup> | BUS State | RXD <sup>(1)</sup> |

|---------------------------|--------------------|---------------------|---------------------|-----------|--------------------|

| L                         | L                  | Н                   | L                   | Domiant   | L                  |

| H or Open                 | L                  | 0.5V <sub>CC</sub>  | 0.5V <sub>CC</sub>  | Recessive | Н                  |

| X                         | H or Open          | GND                 | GND                 | Recessive | Н                  |

(1) H=high level; L=low level; X=irrelevant

#### Table 3. Receiver Function Table

| V <sub>ID</sub> =CANH-CANL | RXD <sup>(1)</sup> | Bus State <sup>(1)</sup> |

|----------------------------|--------------------|--------------------------|

| V <sub>ID</sub> ≥0.9V      | L                  | Dominate                 |

| 0.5< V <sub>ID</sub> <0.9V | ?                  | ?                        |

| V <sub>ID</sub> ≤0.5V      | Н                  | Recessive                |

| Open                       | Н                  | Recessive                |

(1) H=high-level; L=low-level; ?=uncertain

#### Table 4. Under-voltage protection status table

| Vcc                                    | <b>V</b> IO <sup>(1)</sup> | BUS State       | BUS Output <sup>(2)</sup> | RXD <sup>(2)</sup> |

|----------------------------------------|----------------------------|-----------------|---------------------------|--------------------|

| $V_{CC} > V_{uvd_VCC}$                 | $V_{IO}$ > $V_{uvd_VIO}$   | normal          | According to STB and TXD  | Follow Bus         |

| V <sub>CC</sub> < V <sub>uvd_VCC</sub> | $V_{IO} > V_{uvd_VIO}$     | Protected state | GND                       | Н                  |

| V <sub>CC</sub> > V <sub>uvd_VCC</sub> | $V_{IO} < V_{uvd_VIO}$     | Protected state | Z                         | Н                  |

| V <sub>CC</sub> < V <sub>uvd_VCC</sub> | $V_{IO} < V_{uvd_VIO}$     | Protected state | Z                         | Н                  |

1 Only TJA1042T/3

2 H=High Level; Z=High impedance;

### 22. Additional Description

### **Operating Modes**

| Mode    | Pin STB | Pin RXD                  |                             |  |  |  |

|---------|---------|--------------------------|-----------------------------|--|--|--|

| MODE    |         | LOW                      | HIGH                        |  |  |  |

| Common  | LOW     | bus dominant             | bus recessive               |  |  |  |

| Standby | HIGH    | wake-up request detected | no wake-up request detected |  |  |  |

#### Common Mode

A LOW level on pin STB selects Normal mode. In this mode, the transceiver can transmit and receive data via the bus lines CANH and CANL (see Figure 1 for the block diagram). The differential receiver converts the analog data on the bus lines into digital data which is output to pin RXD. The slopes of the output signals on the bus lines are controlled internally and are optimized in a way that guarantees the lowest possible EME.

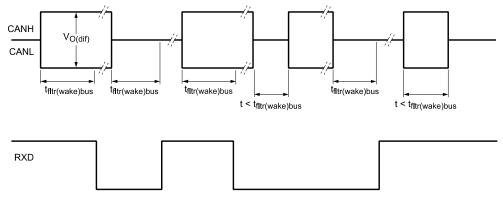

#### **Standby Mode**

A HIGH level on pin STB selects Standby mode. In Standby mode, the transceiver is not able to transmit or correctly receive data via the bus lines. The transmitter and Normal-mode receiver blocks are switched off to reduce supply current, and only a low-power differential receiver monitors the bus lines for activity. The wake-up filter on the output of the low-power receiver does not latch bus dominant states, but ensures that only bus dominant and bus recessive states that persist longer than t<sub>fitr(wake)bus</sub> are reflected on pin RXD.

In Standby mode, the bus lines are biased to ground to minimize the system supply current. The low-power receiver is supplied by  $V_{1O}$ , and is capable of detecting CAN bus activity even if  $V_{1O}$  is the only supply voltage available. When pin RXD goes LOW to signal a wake-up request, a transition to Normal mode will not be triggered until STB is forced LOW.

### **Current protection**

A current-limiting circuit protects the transmitter output stage from damage caused by accidental short-circuit to either positive or negative supply voltage, although power dissipation increases during this fault condition.

### **Over temperature protection**

The output drivers are protected against over-temperature conditions. If the virtual junction temperature exceeds the shutdown junction temperature  $T_{j(sd)}$ , the output drivers will be disabled until the virtual junction temperature becomes lower than  $T_{j(sd)}$  and TXD becomes recessive again.

By including the TXD condition, the occurrence of output driver oscillation due to temperature drifts is avoided.

#### **TXD** dominant time-out function

A 'TXD dominant time-out' timer is started when pin TXD is set LOW. If the LOW state on pin TXD persists for longer than  $t_{to(dom)TXD}$ , the transmitter is disabled, releasing the bus lines to recessive state. This function prevents a hardware and/or software application failure from driving the bus lines to a permanent dominant state (blocking all network communications). The TXD dominant time-out timer is reset when pin TXD is set to HIGH. The TXD dominant time-out time also defines the minimum possible bit rate of 40 kbit/s.

### Undervoltage detection on pins $V_{CC}$ and $V_{IO}$

Should  $V_{CC}$  drop below the  $V_{CC}$  undervoltage detection level,  $V_{uvd(VCC)}$ , the transceiver will switch to Standby mode. The logic state of pin STB will be ignored until  $V_{CC}$  has recovered.

Should  $V_{IO}$  drop below the  $V_{IO}$  undervoltage detection level,  $V_{uvd(VIO)}$ , the transceiver will switch off and disengage from the bus (zero load) until  $V_{IO}$  has recovered.

## 23. Test Circuit

# © Shenzhen Fulihao Science & Technology Co., Ltd.

TJA1042

Interfaces

# 24. Package Outlines

## 25. Disclaimers

### Limited warranty and liability

Information in this document is believed to be accurate and reliable. However, Fulihao does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. It is the customer's responsibility to validate that a particular product with the properties described in the product specification is suitable for use in a particular application.

### Suitability for use

Fulihao products are designed for specific applications and should not be used for any purpose (including, without limitation, automotive, aerospace, medical, life-saving applications, or any other application which requires especially high reliability for the prevention of such defect as may directly cause damage to the third party's life, body or property) not expressly set forth in applicable Fulihao product documentation.

### **Right to make changes**

Fulihao reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. Reproduction in whole or in part is prohibited without the prior written consent of the copyright owner. Fulihao takes no responsibility for the content in this document if provided by an information source outside of Fulihao. This document supersedes and replaces all information supplied prior to the publication hereof.