# 2EDL05 family

# 2EDL05x06xx family

### 600 V Half Bridge Gate Driver with Integrated Bootstrap Diode (BSD)

### Features

- Infineon thin-film-SOI-technology

- Fully operational to +600 V

- Floating channel designed for bootstrap operation

- Output source/sink current capability +0.36 A/-0.7 A

- Integrated Ultra-fast, low *R*<sub>DS(ON)</sub> Bootstrap Diode

- Tolerant to negative transient voltage up to -100 V (Pulse width is up 300 ns) given by SOI-technology

- 10 ns typ., 60 ns max. propagation delay matching

- dV/dt immune ±50 V

- Gate drive supply range from 10 V to 20 V

- Undervoltage lockout for both channels

- 3.3 V, 5 V and 15 V input logic compatible

- RoHS compliant

### **Potential applications**

- Motor drives, General purpose inverters

- Refrigeration compressors, home appliance

- Half-bridge and full-bridge converters in offline AC-DC power supplies for telecom and lighting

### **Product validation**

Qualified for industrial applications according to the relevant tests of JEDEC47/20/22.

### Description

The 2ED05 is a 600-V half-bridge gate driver family. Its Infineon thin-film-SOI technology provides excellent ruggedness and noise immunity. The Schmitt trigger logic inputs are compatible with standard CMOS or LSTTL logic down to 3.3 V. The output drivers features a high pulse current buffer stage designed for minimum driver cross-conduction. The floating channel can be used to drive an N-channel power MOSFET or IGBT in the high side configuration which operates up to 600 V. Additionally, the offline clamping function provides an inherent protection of the parasitic turn-on by floating gate conditions when IC is not supplied.

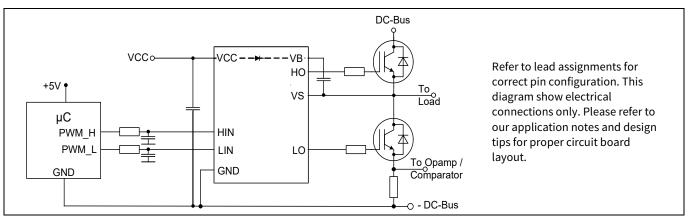

Figure 1 Typical application diagram

### Product summary

| V <sub>OFFSET</sub>                          |

|----------------------------------------------|

| I <sub>0+/-</sub> (typ.)                     |

| V <sub>OUT</sub>                             |

| Delay Matching                               |

| <i>t</i> <sub>f</sub> /t <sub>r</sub> (typ.) |

### Package

DSO-14 DSO-8

= 620 V max.

= 0.36 A/0.7 A

= 10 V - 17.5 V

= 60 ns max.

= 24 ns/48 ns

### **Ordering information**

| Sales Name         | Special<br>function | output<br>current | Target<br>transistor | typ. LS UVLO-<br>thresholds | Bootstrap<br>diode | Package | Evaluation board |                 |  |        |                  |

|--------------------|---------------------|-------------------|----------------------|-----------------------------|--------------------|---------|------------------|-----------------|--|--------|------------------|

| 2EDL05I06PF        | deadtime,           |                   |                      |                             |                    | DSO-8   |                  |                 |  |        |                  |

| <u>2EDL05I06PJ</u> | interlock           |                   | IGBT                 | IGBT                        | IGBT               | IGBT    | IGBT             | 12.5 V / 11.6 V |  | DSO-14 | EVAL-2EDL05I06PF |

| 2EDL05I06BF        | 1                   | 0.5 A             |                      |                             | Yes                | DSO-8   |                  |                 |  |        |                  |

| 2EDL05N06PF        | deadtime,           |                   | MOCEET               | 0.11/0.21/                  |                    | DSO-8   |                  |                 |  |        |                  |

| <u>2EDL05N06PJ</u> | interlock           |                   | MOSFET               | 9.1 V / 8.3 V               |                    | DSO-14  |                  |                 |  |        |                  |

### **Table of contents**

| Featu       | ıres                                                   | 1 |

|-------------|--------------------------------------------------------|---|

| Prod        | uct summary                                            | 1 |

| Packa       | age                                                    | 1 |

| Poter       | ntial applications                                     | 1 |

| Prod        | uct validation                                         | 1 |

| Desci       | ription                                                | 1 |

| Orde        | ring information                                       | 2 |

|             | of contents                                            |   |

| 1           | Block diagram                                          |   |

| 2           | Lead definitions                                       |   |

| 3           | Functional description                                 |   |

| <b>3</b> .1 | Low Side and High Side Control Pins (LIN, HIN)         |   |

| 3.1.1       | Input voltage range                                    |   |

| 3.1.2       | Switching levels                                       |   |

| 3.1.3       | Input filter time                                      |   |

| 3.2         | VDD and GND                                            |   |

| 3.3         | VB and VS (High Side Supplies)                         | 5 |

| 3.4         | LO and HO (Low and High Side Outputs)                  | 5 |

| 3.5         | Undervoltage lockout (UVLO)                            | 5 |

| 3.6         | Bootstrap diode                                        |   |

| 3.7         | Deadtime and interlock function                        |   |

| 3.8         | Tolerant to negative transient voltage on VS pin (-VS) | 6 |

| 4           | Electrical parameters                                  | 9 |

| 4.1         | Absolute maximum ratings                               | 9 |

| 4.2         | Required operation conditions1                         | 0 |

| 4.3         | Operating Range1                                       |   |

| 4.4         | Static logic function table1                           |   |

| 4.5         | Static parameters1                                     |   |

| 4.6         | Dynamic parameters1                                    | 3 |

| 5           | Timing diagrams1                                       | 4 |

| 6           | Package information1                                   | 7 |

| 7           | Qualification information1                             | 9 |

| 8           | Related products1                                      | 9 |

| Revis       | ion history2                                           | 0 |

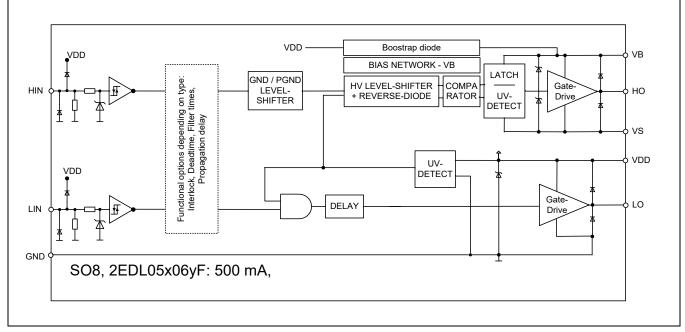

### 1 Block diagram

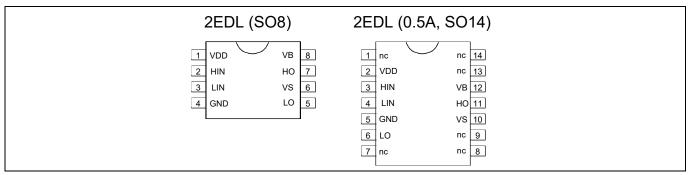

### 2 Lead definitions

| Table 1 | 2EDL05 family lead definitions |

|---------|--------------------------------|

|---------|--------------------------------|

| Pin no. | Name | Function                                                                                                          |

|---------|------|-------------------------------------------------------------------------------------------------------------------|

| 1       | VDD  | Low-side and logic supply voltage                                                                                 |

| 2       | HIN  | Logic input for high-side gate driver output (HO), in phase. Schmitt trigger inputs with hysteresis and pull down |

| 3       | LIN  | Logic input for low-side gate driver output (LO), in phase. Schmitt trigger inputs with hysteresis and pull down  |

| 4       | GND  | Low-side gate drive return                                                                                        |

| 5       | LO   | Low-side driver output                                                                                            |

| 6       | VS   | High voltage floating supply return                                                                               |

| 7       | НО   | High-side driver output                                                                                           |

| 8       | VB   | High-side gate drive floating supply                                                                              |

### 3 Functional description

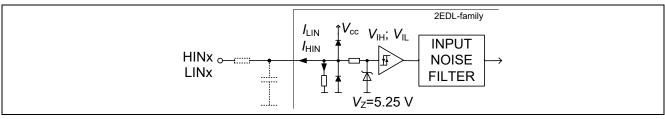

### 3.1 Low Side and High Side Control Pins (LIN, HIN)

### 3.1.1 Input voltage range

All input pins have the capability to process input voltages up to the supply voltage of the IC. The inputs are therefore internally clamped to VDD and GND by diodes. An internal pull-down resistor is high ohmic, so that it can keep the IC in a safe state in case of PCB crack.

### 3.1.2 Switching levels

The Schmitt trigger input threshold is such to guarantee LSTTL and CMOS compatibility down to 3.3 V controller outputs. The input Schmitt trigger and noise filter provide beneficial noise rejection to short input pulses according to Figure 4 and Figure 5. Please note, that the switching levels of the input structures remain constant even though they can accept amplitudes up to the IC supply level.

Figure 4 Input pin structure

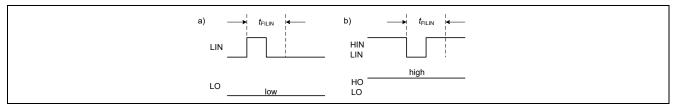

### 3.1.3 Input filter time

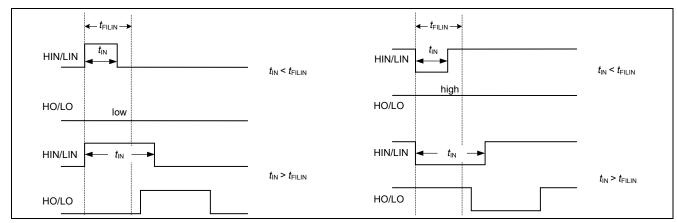

### Figure 5 Input filter timing diagram

Short pulses are suppressed by means of an input filter. All IC, which have undervoltage lockout (UVLO) thresholds for MOSFET, have an input filter time of  $t_{\text{FILIN}}$  = 75 ns typ. and 150 ns max. All IC having UVLO thresholds for IGBT have filter times of  $t_{\text{FILIN}}$  = 150 ns min and 200 ns typ.

### 3.2 VDD and GND

VDD is the low side supply and it provides power to both the input logic and the low side output power stage. The input logic is referenced to GND ground as well as the under-voltage detection circuit. Output power stage is also referenced to GND ground.

The undervoltage lockout circuit enables the device to operate at power on when a typical supply voltage higher than  $V_{DDUV+}$  is present. Please see section 3.5 "Undervoltage lockout" for further information.

A filter time of typ. 1.8µs<sup>1</sup> helps to suppress noise from the UVLO circuit, so that negative going voltage spikes at the supply pins will avoid parasitic UVLO events.

### 3.3 VB and VS (High Side Supplies)

VB to VS is the high side supply voltage. The high side circuit can float with respect to GND following the external high side power device emitter/source voltage. Due to the low power consumption, the floating driver stage can be supplied by bootstrap topology connected to VDD. A filter time of typ. 1.8µs<sup>1</sup> helps to suppress noise from the UVLO circuit, so that negative going voltage spikes at the supply pins will avoid parasitic UVLO events.

The under-voltage circuit enables the device to operate at power on when a typical supply voltage higher than  $V_{DDUV+}$  is present. Please see section 3.5 "Undervoltage lockout" for further information. Details on bootstrap supply section and transient immunity can be found in application note <u>EiceDRIVER<sup>TM</sup> 2EDL family: Technical description</u>.

### 3.4 LO and HO (Low and High Side Outputs)

Low side and high side power outputs are specifically designed for pulse operation such as gate drive for IGBT and MOSFET devices. Low side output is state triggered by the respective input, while high side output is edge triggered by the respective input. In particular, after an undervoltage condition of the VBS supply, a new turn-on signal (edge) is necessary to activate the high side output. In contrast, the low side outputs switch to the state of their respective inputs after an undervoltage condition of the VDD supply.

The output current specification  $I_{0+}$  and  $I_{0-}$  is defined in a way, which considers the power transistors miller voltage. This helps to design the gate drive better in terms of the application needs. Nevertheless, the devices are also characterised for the value of the pulse short circuit value  $I_{0pk+}$  and  $I_{0pk-}$ .

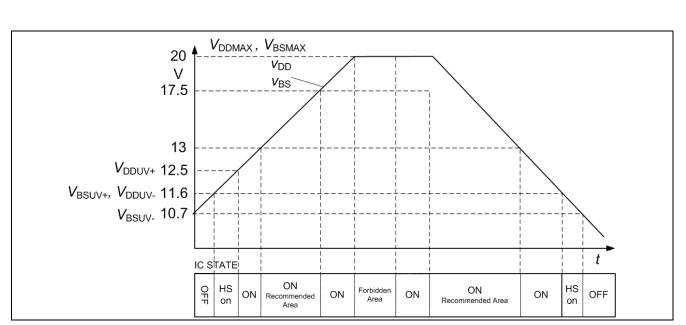

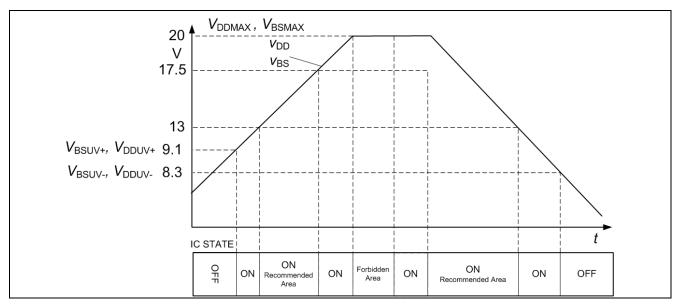

### 3.5 Undervoltage lockout (UVLO)

Two different UVLO options are required for IGBT and MOSFET. The types 2EDL05I06Px and 2EDL05I06BF are designed to drive IGBT. There are higher levels of undervoltage lockout for the low side UVLO than for the high side. This supports an improved start up of the IC, when bootstrapping is used. The thresholds for the low side are typically  $V_{DDUV+} = 12.5 \text{ V}$  (positive going) and  $V_{DDUV-} = 11.6 \text{ V}$  (negative going). The thresholds for the high side are typically  $V_{BSUV+} = 11.6 \text{ V}$  (positive going) and  $V_{BSUV-} = 10.7 \text{ V}$  (negative going).

The types 2EDL05N06Px are designed to drive power MOSFET. A similar distinction for the high side and low side UVLO threshold as for IGBT is not realised here. The IC shuts down all the gate drivers power outputs, when the supply voltage is below typ.  $V_{DDUV-} = 8.3 V (min. / max. = 7.5 V / 9 V)$ . The turn-on threshold is typ.  $V_{DDUV+} = 9.1 V (min. / max. = 8.3 V / 9.9 V)$

### 3.6 Bootstrap diode

An ultra fast bootstrap diode is monolithically integrated for establishing the high side supply. The differential resistor of the diode helps to avoid extremely high inrush currents when charging the bootstrap capacitor initially.

www.infineon.com/gdHalfBridge

<sup>&</sup>lt;sup>1</sup> Not subject of production test, verified by characterisation 2EDL05 family Datasheet

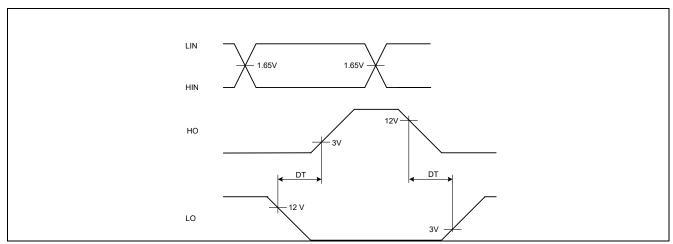

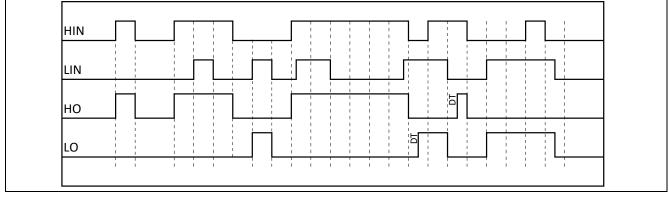

### 3.7 Deadtime and interlock function

The IC provides a hardware fixed deadtime. The deadtime is different for the two MOSFET types (2EDL05N06Px) and for the two IGBT types (2EDL05I06Px). The deadtimes are particularly typ. 380 ns for IGBT and typ. 75 ns for MOSFET. An additional interlock function prevents the two outputs from being activated simultaneously.

The part 2EDL05I06BF does not have the deadtime feature and also not the interlock function. Here, the two outpus can be activated simultaneously.

### 3.8 Tolerant to negative transient voltage on VS pin (-VS)

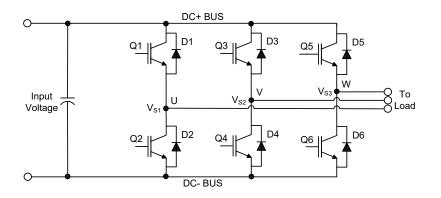

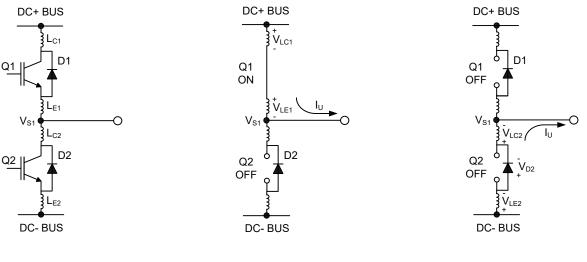

A common problem in today's high-power switching converters is the transient response of the switch node's voltage as the power switches transition on and off quickly while carrying a large current. A typical three phase inverter circuit is shown in Figure 6; here we define the power switches and diodes of the inverter.

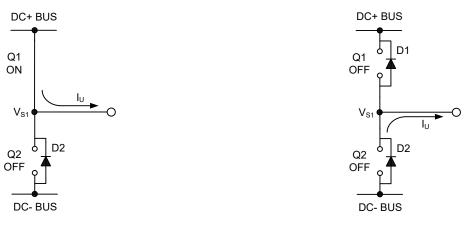

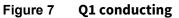

If the high-side switch (e.g., the IGBT Q1 in Figures 7 and 8) switches off, while the U phase current is flowing to an inductive load, a current commutation occurs from high-side switch (Q1) to the diode (D2) in parallel with the low-side switch of the same inverter leg. At the same instance, the voltage node V<sub>s1</sub>, swings from the positive DC bus voltage to the negative DC bus voltage.

Figure 6 Three phase inverter

Figure 8 D2 conducting

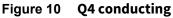

Also when the V phase current flows from the inductive load back to the inverter (see Figures 9 and 10), and Q4 IGBT switches on, the current commutation occurs from D3 to Q4. At the same instance, the voltage node,  $V_{52}$ , swings from the positive DC bus voltage to the negative DC bus voltage.

Figure 9 D3 conducting

However, in a real inverter circuit the  $V_s$  voltage swing does not stop at the level of the negative DC bus but instead swings below the level of the negative DC bus. This undershoot voltage is called "negative transient voltage".

The circuit shown in Figure 11 depicts one leg of the three phase inverter; Figures 12 and 13 show a simplified illustration of the commutation of the current between Q1 and D2. The parasitic inductances in the power circuit from the die bonding to the PCB tracks are lumped together in  $L_c$  and  $L_E$  for each IGBT. When the high-side switch is on,  $V_{S1}$  is below the DC+ voltage by the voltage drops associated with the power switch and the parasitic elements of the circuit. When the high-side power switch turns off, the load current momentarily flows in the low-side freewheeling diode due to the inductive load connected to  $V_{S1}$  (the load is not shown in these figures). This current flows from the DC- bus (which is connected to the COM pin of the HVIC) to the load and a negative voltage between  $V_{S1}$  and the DC- Bus is induced (i.e., the COM pin of the HVIC is at a higher potential than the VS pin).

Figure 11 Parasitic Elements

Figure 12 VS positive

Figure 13 VS negative

In a typical motor drive system, dV/dt is typically designed to be in the range of 3-5 V/ns. The negative V<sub>s</sub> transient voltage can exceed this range during some events such as short circuit and over-current shutdown, when di/dt is greater than in normal operation.

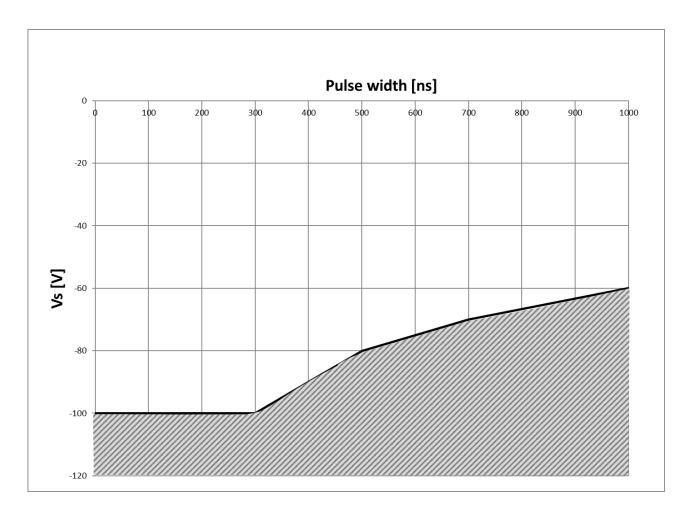

Infineon's HVICs have been designed for the robustness required in many of today's demanding applications. An indication of the 2EDL05 family's robustness can be seen in Figure 14, where the 2EDL05 Safe Operating Area is shown at  $V_{BS}$ =15 V based on repetitive negative  $V_S$  spikes. A negative transient voltage falling in the grey area

(outside SOA) may lead to IC permanent damage; viceversa unwanted functional anomalies or permanent damage to the IC do not appear if negative VS transients fall inside the SOA.

### Figure 14 Negative transient voltage SOA on VS pin for 2EDL05 family @ VBS=15 V

Even though the 2EDL05 family has been shown to be able to handle these large negative transient voltage conditions, it is highly recommended that the circuit designer always limit the negative transient voltage on VS pin as much as possible by careful PCB layout and component use.

### 4 Electrical parameters

### 4.1 Absolute maximum ratings

All voltages are absolute voltages referenced to  $V_{GND}$  -potential unless otherwise specified. ( $T_a=25^{\circ}C$ ).

#### Table 2 Absolute maximum ratings

| Parameter                                                             |                         | Symbol               | Min.                                      | Max.                         | Unit |

|-----------------------------------------------------------------------|-------------------------|----------------------|-------------------------------------------|------------------------------|------|

| High side offset voltage <sup>1</sup>                                 |                         | Vs                   | V <sub>DD</sub> -V <sub>BS</sub> -6       | 600                          | V    |

| High side offset voltage ( <i>t</i> <sub>p</sub> <300ns) <sup>1</sup> |                         |                      | V <sub>DD</sub> -V <sub>BS</sub> -<br>100 | -                            |      |

| High side offset voltage <sup>1</sup>                                 |                         | VB                   | V <sub>DD</sub> – 6                       | 620                          |      |

| High side offset voltage ( <i>t</i> <sub>p</sub> <300ns) <sup>1</sup> |                         |                      | V <sub>DD</sub> – 100                     | -                            |      |

| High side floating supply voltage ( $V_{\rm B}$ vs. clamped)          | <i>V</i> s) (internally | $V_{\rm BS}$         | -1                                        | 20                           |      |

| High side output voltage ( $V_{\rm HO}$ vs. $V_{\rm S}$ )             | V <sub>HO</sub>         | -0.5                 | V <sub>B</sub> + 0.5                      | ).5                          |      |

| Low side supply voltage (internally clam                              | iped)                   | V <sub>DD</sub>      | -1                                        | 20                           |      |

| Low side output voltage ( $V_{ m LO}$ vs. $V_{ m GND}$ )              |                         | $V_{\rm LO}$         | -0.5                                      | $V_{\rm GND}$ + 0.5          |      |

| Input voltage LIN,HIN                                                 |                         | $V_{\rm IN}$         | -0.5                                      | <i>V</i> <sub>DD</sub> + 0.5 |      |

| Power dissipation (to package) <sup>2</sup>                           | DSO8<br>DSO14           | PD                   |                                           | 0.6<br>0.85                  | W    |

| Thermal resistance<br>(junction to ambient, see section 6)            | DSO8<br>DSO14           | R <sub>th(j-a)</sub> |                                           | 195<br>139                   | K/W  |

| Junction temperature <sup>3</sup>                                     |                         | $T_{ m J}$           | _                                         | 150                          | °C   |

| Storage temperature                                                   |                         | Ts                   | - 40                                      | 150                          |      |

| offset voltage slew rate <sup>4</sup>                                 |                         | dV <sub>s</sub> /dt  | _                                         | 50                           | V/ns |

$<sup>^{1}</sup>$  In case V<sub>DD</sub> > V<sub>B</sub> there is an additional power dissipation in the internal bootstrap diode between pins VDD and VB in case of activated bootstrap diode. Insensitivity of bridge output to negative transient voltage up to -100V is not subject to production test – verified by design / characterization.

<sup>&</sup>lt;sup>2</sup> Consistent power dissipation of all outputs. All parameters are inside operating range.

<sup>&</sup>lt;sup>3</sup> Qualification stress tests cover a max. junction temperature of 150°C for 1000 h.

<sup>&</sup>lt;sup>4</sup> Not subject of production test, verified by characterisation.

### 4.2 **Required operation conditions**

All voltages are absolute voltages referenced to  $V_{GND}$  -potential unless otherwise specified. ( $T_a$ =25°C).

#### Table 3 Required Operation Conditions

| Parameter                                    | Symbol          | Min. | Max. | Unit |

|----------------------------------------------|-----------------|------|------|------|

| High side offset voltage <sup>1</sup>        | $V_{\rm B}$     | 7    | 620  | V    |

| Low side supply voltage (internally clamped) | V <sub>DD</sub> | 10   | 20   |      |

### 4.3 Operating Range

All voltages are absolute voltages referenced to  $V_{GND}$  -potential unless otherwise specified. ( $T_a=25^{\circ}C$ )

#### Table 4Operating range

| Parameter                                                                |                 | Symbol                                  | Min.            | Max.       | Unit |

|--------------------------------------------------------------------------|-----------------|-----------------------------------------|-----------------|------------|------|

| High side floating supply offset voltage                                 | Vs              | V <sub>DD</sub> - V <sub>BS</sub><br>-1 | 500             | V          |      |

| High side floating supply offset voltage ( $V_{\rm B}$ vs. $V_{\rm DE}$  | $V_{\rm BDD}$   | -1.0                                    | 500             | ]          |      |

| High side floating supply voltage $(V_{\rm B} \text{ vs. } V_{\rm S})^1$ | IGBT-Types      | $V_{\rm BS}$                            | 13              | 17.5       | ]    |

|                                                                          | MOSFET-Types    |                                         | 10              | 17.5       | ]    |

| High side output voltage (V <sub>HO</sub> vs. V <sub>S</sub> )           | V <sub>HO</sub> | 0                                       | V <sub>BS</sub> | ]          |      |

| Low side output voltage ( $V_{ m LO}$ vs. $V_{ m GND}$ )                 | $V_{\rm LO}$    | 0                                       | V <sub>DD</sub> | ]          |      |

| Low side supply voltage                                                  | IGBT-Types      | V <sub>DD</sub>                         | 13              | 17.5       | 1    |

|                                                                          | MOSFET-Types    |                                         | 10              | 17.5       | 1    |

| Logic input voltages LIN,HIN <sup>2</sup>                                | ·               | $V_{\rm IN}$                            | 0               | 17.5       |      |

| Pulse width for ON or OFF <sup>3</sup>                                   | IGBT-Types      | t <sub>IN</sub>                         | 0.8             | -          | μs   |

|                                                                          | MOSFET-Types    |                                         | 0.3             | -          | 1    |

| Ambient temperature                                                      |                 |                                         | -40             | 105        | °C   |

| Thermal coefficient<br>(junction to top, see section 6)                  | DSO8<br>DSO14   | $\Psi_{	ext{th(j-top)}}$                | _               | 8.0<br>6.0 | K/W  |

$<sup>^1</sup>$  Logic operational for  $V_B$  (V\_B vs.  $V_{GND}) > 7.0$  V.

<sup>&</sup>lt;sup>2</sup> All input pins (HIN, LIN) are internally clamped (see abs. maximum ratings).

<sup>&</sup>lt;sup>3</sup> The input pulse may not be transmitted properly in case of input pulse width at LIN and HIN below 0.8µs (IGBT types) or 0.3 µs (MOSFET) respectively.

### 4.4 Static logic function table

| VDD                  | VBS               | LO  | но  |

|----------------------|-------------------|-----|-----|

| <v<sub>DDUV-</v<sub> | Х                 | 0   | 0   |

| 15V                  | $< V_{\rm BSUV-}$ | LIN | 0   |

| 15V                  | 15V               | 0   | 0   |

| 15V                  | 15V               | 0   | 0   |

| 15V                  | 15V               | LIN | HIN |

all voltages with reference to GND

### 4.5 Static parameters

$V_{DD} = V_{BS} = 15V$  unless otherwise specified. ( $T_a = 25^{\circ}$ C).

#### Table 5Static parameters

| Parameter                                                           |              | Symbol              | Values |                                                |                                              | Unit | Test                                         |  |

|---------------------------------------------------------------------|--------------|---------------------|--------|------------------------------------------------|----------------------------------------------|------|----------------------------------------------|--|

|                                                                     |              |                     | Min.   | Тур.                                           | Max.                                         |      | condition                                    |  |

| High level input voltage                                            |              | $V_{\mathrm{IH}}$   | 1.7    | 2.1                                            | 2.4                                          | V    |                                              |  |

| Low level input voltage                                             |              | V <sub>IL</sub>     | 0.7    | 0.9                                            | 1.1                                          |      |                                              |  |

| High level output voltage                                           | LO<br>HO     | V <sub>OH</sub>     | -      | V <sub>DD</sub> -0.45<br>V <sub>B</sub> -0.45  | V <sub>DD</sub> -1<br>V <sub>B</sub> -1      |      | <i>I</i> o = - 20 mA                         |  |

| Low level output voltage                                            | LO<br>HO     | V <sub>OL</sub>     | -      | V <sub>GND</sub> +0.13<br>V <sub>S</sub> +0.13 | V <sub>GND</sub> +0.3<br>V <sub>S</sub> +0.3 |      | <i>I</i> o = 20 mA                           |  |

| V <sub>DD</sub> supply undervoltage                                 | IGBT-types   | $V_{\rm DDUV^+}$    | 11.8   | 12.5                                           | 13.2                                         |      |                                              |  |

| positive going threshold                                            | MOSFET types | ]                   | 8.3    | 9.1                                            | 9.9                                          |      |                                              |  |

| V <sub>BS</sub> supply undervoltage                                 | IGBT-types   | $V_{\rm BSUV^+}$    | 10.9   | 11.6                                           | 12.4                                         |      |                                              |  |

| positive going threshold                                            | MOSFET types |                     | 8.3    | 9.1                                            | 9.9                                          |      |                                              |  |

| <i>V</i> <sub>DD</sub> supply undervoltage negative going threshold | IGBT-types   | V <sub>DDUV-</sub>  | 10.9   | 11.6                                           | 12.4                                         |      |                                              |  |

|                                                                     | MOSFET types |                     | 7.5    | 8.3                                            | 9                                            |      |                                              |  |

| V <sub>BS</sub> supply undervoltage                                 | IGBT-types   | V <sub>BSUV-</sub>  | 10     | 10.7                                           | 11.7                                         |      |                                              |  |

| negative going threshold                                            | MOSFET types |                     | 7.5    | 8.3                                            | 9                                            |      |                                              |  |

| $V_{\rm DD}$ and $V_{\rm BS}$ supply UVLO                           | IGBT-types   | VDDUVH              | 0.5    | 0.9                                            | -                                            |      |                                              |  |

| hysteresis                                                          | MOSFET types | VBSUVH              | 0.5    | 0.9                                            | -                                            |      |                                              |  |

| High side leakage current<br>GND                                    | betw. VS and | I <sub>LVS+</sub>   | -      | 1                                              | 12.5                                         | μA   | <i>V</i> <sub>S</sub> = 600V                 |  |

| High side leakage current betw. VS and GND                          |              | I <sub>LVS+</sub> 1 | -      | 10                                             | -                                            |      | $T_{\rm J}$ = 125 °C,<br>$V_{\rm S}$ = 600 V |  |

| Quiescent current $V_{\rm BS}$ supply (VB only)                     |              | I <sub>QBS1</sub>   | -      | 170                                            | 300                                          |      | HO = low<br>depending o<br>current types     |  |

| Quiescent current $V_{\rm BS}$ supply (VB only)                     |              | I <sub>QBS2</sub>   | -      | 170                                            | 300                                          |      | HO = high<br>depending o<br>current type     |  |

| Quiescent current VDD supply (VDD only)                             |              | I <sub>QDD1</sub>   | -      | 0.3                                            | 0.6                                          | mA   | $V_{\rm LIN}$ = float.                       |  |

<sup>1</sup> Not subject of production test, verified by characterisation 2EDL05 family Datasheet www.infineon.com/gdHalfBridge

#### Table 5Static parameters

| Parameter                                                                                     | Symbol                 | l Values |      |      | Unit | Test                                               |

|-----------------------------------------------------------------------------------------------|------------------------|----------|------|------|------|----------------------------------------------------|

|                                                                                               |                        | Min.     | Тур. | Max. |      | condition                                          |

| Quiescent current VDD supply (VDD only)                                                       | I <sub>QDD2</sub>      | -        | 0.28 | 0.6  |      | V <sub>LIN</sub> = 3.3 V,<br>V <sub>HIN</sub> =0   |

| Quiescent current VDD supply (VDD only)                                                       | I <sub>QDD3</sub>      | -        | 0.28 | 0.6  |      | V <sub>LIN</sub> =0 , V <sub>HIN</sub> =3.3 V      |

| Input bias current                                                                            | $I_{\rm LIN^+}$        | 15       | 35   | 60   | μΑ   | <i>V</i> <sub>LIN</sub> = 3.3 V                    |

| Input bias current                                                                            | $I_{\rm LIN-}$         | -        | 0    | -    |      | $V_{\rm LIN} = 0$                                  |

| Input bias current                                                                            | $I_{\rm HIN^+}$        | 15       | 35   | 60   |      | <i>V</i> <sub>HIN</sub> = 3.3 V                    |

| Input bias current                                                                            | $I_{\rm HIN-}$         | -        | 0    | -    |      | <i>V</i> <sub>HIN</sub> = 0                        |

| Mean output current for load capacity<br>charging in range from 3 V (20%) to 6 V<br>(40%)     | <i>I</i> <sub>O+</sub> | 0.18     | 0.23 | -    | A    | C <sub>L</sub> = 22 nF                             |

| Peak output current turn on (single pulse)                                                    | I <sub>Opk+</sub> 1    | -        | 0.36 | -    |      | R <sub>L</sub> = 0 Ω, $t_p$ <10 µs                 |

| Mean output current for load capacity<br>discharging in range from 12 V (80%) to 9 V<br>(60%) | <i>I</i> <sub>0-</sub> | 0.39     | 0.48 | -    |      | C∟= 22 nF                                          |

| Peak output current turn off (single pulse)                                                   | I <sub>Opk-</sub> 1    | -        | 0.70 | -    |      | $R_{\rm L}$ = 0 $\Omega$ , $t_{\rm p}$ <10 $\mu$ s |

| Bootstrap diode forward voltage between<br>VDD and VB                                         | V <sub>F,BSD</sub>     | -        | 1.0  | 1.2  | V    | <i>I</i> <sub>F</sub> = 0.3 mA                     |

| Bootstrap diode forward current between<br>VDD and VB                                         | I <sub>F,BSD</sub>     | 30       | 55   | 80   | mA   | $V_{\rm DD} - V_B$ = 4 V                           |

| Bootstrap diode resistance                                                                    | $R_{\rm BSD}$          | 20       | 36   | 54   | Ω    | $V_{F1} = 4 V, V_{F2} = 5 V$                       |

<sup>&</sup>lt;sup>1</sup> Not subject of production test, verified by characterisation 2EDL05 family Datasheet www.infineon.com/gdHalfBridge

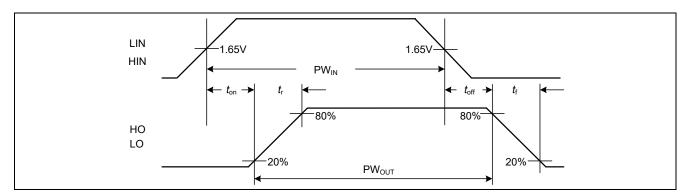

### 4.6 Dynamic parameters

$V_{DD} = V_{BS} = 15 \text{ V}, V_S = V_{GND}, C_L = 180 \text{ pF}$  unless otherwise specified. ( $T_a=25^{\circ}\text{C}$ ).

#### Table 6Dynamic parameters

| Parameter                                     |                            | Symbol                    |           | Value      | s          | Unit | Test                                     |  |

|-----------------------------------------------|----------------------------|---------------------------|-----------|------------|------------|------|------------------------------------------|--|

|                                               |                            |                           | Min.      | Тур.       | Max.       |      | condition                                |  |

| Turn-on propagation                           | IGBT types                 | ton                       | 280       | 420        | 610        | ns   | $V_{\text{LIN/HIN}} = 0 \text{ or } 3.3$ |  |

| delay                                         | MOSFET types               |                           | 210       | 310        | 460        |      | V                                        |  |

| Turn-off propagation                          | IGBT types                 | t <sub>off</sub>          | 260       | 400        | 590        |      |                                          |  |

| delay                                         | MOSFET types               | -                         | 200       | 300        | 440        |      |                                          |  |

| Turn-on rise time                             |                            | tr                        | -         | 48         | 80         |      | $V_{\text{LIN/HIN}} = 0 \text{ or } 3.3$ |  |

| Turn-off fall time                            |                            | tf                        | -         | 24         | 40         |      | V<br>C∟=1 nF                             |  |

| Input filter time at                          | IGBT types                 | <i>t</i> <sub>FILIN</sub> | 120       | 192        | -          |      | <i>V</i> <sub>LIN/HIN</sub> = 0 & 3.3    |  |

| LIN/HIN for turn on and off                   | MOSFET types<br>HIN<br>LIN |                           | 50<br>100 | 100<br>150 | 170<br>250 |      | V                                        |  |

| Dead time                                     | IGBT types                 | DT                        | 260       | 380        | 540        | ns   | $V_{\rm LIN/HIN} = 0 \& 3.3$             |  |

| (not for 2EDL05I06BF)                         | MOSFET types               |                           | 30        | 75         | 140        |      | V                                        |  |

| Dead time matching<br>abs(DT LH – DT HL)      | IGBT types                 | MDT                       | -         | 10         | 80         |      | ext. dead time<br>Ons                    |  |

| for single IC (not for<br>2EDL05I06BF)        | MOSFET types               |                           |           | 10         | 50         |      |                                          |  |

| Matching delay ON, abs(ton_HS - ton_LS)       |                            | MTon                      | -         | 10         | 60         |      | external dead<br>time > 500 ns           |  |

| Matching delay OFF, abs(toff_HS-toff_LS)      |                            | MT <sub>OFF</sub>         | -         | 10         | 60         |      | external dead<br>time >500 ns            |  |

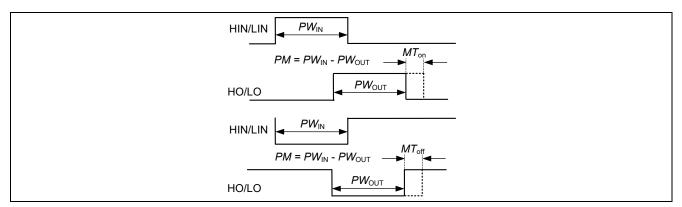

| Output pulse width                            | IGBT types                 | РМ                        | -         | 20         | 80         |      | $PW_{in} > 1 \ \mu s$                    |  |

| matching. PW <sub>in</sub> -PW <sub>out</sub> | MOSFET types               |                           | -         | 20         | 70         |      |                                          |  |

## 5 Timing diagrams

Figure 15 Timing of short pulse suppression

Figure 16 Timing of of internal deadtime

Figure 17 Input to output propagation delay times and switching times definition

Figure 18 Operating areas (IGBT UVLO levels)

Figure 19 Operating areas (MOSFET UVLO levels)

Figure 20 Output pulse width timing and matching delay timing diagram for positive logic

fineon

Figure 21 Deadtime and interlock

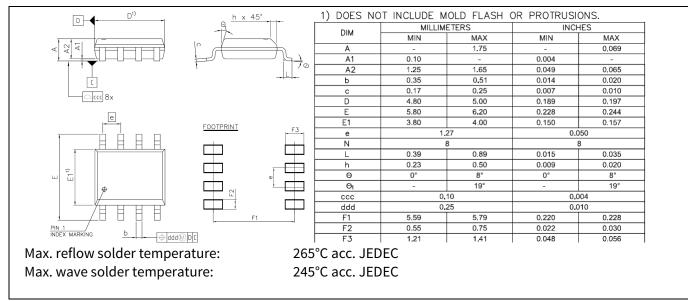

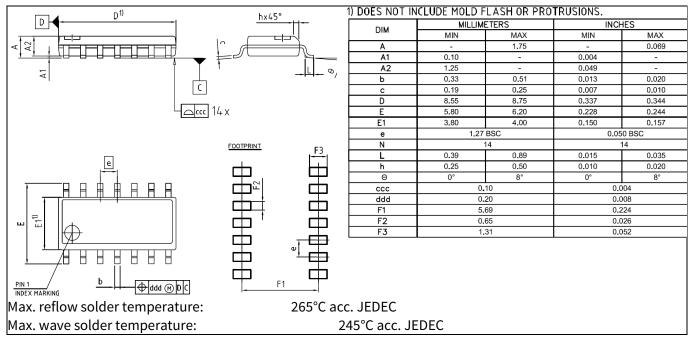

# 6 Package information

Figure 22 Package outline PG-DSO-8

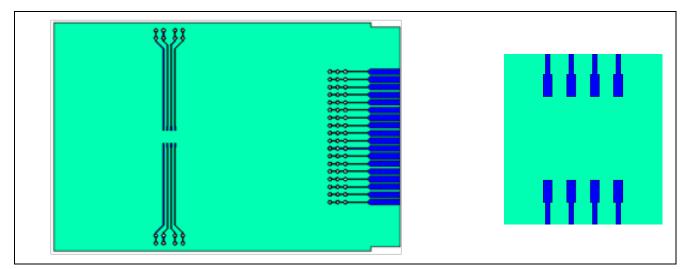

#### Figure 23 PCB reference layout left: Reference layout right: detail of footprint

The thermal coefficient is used to calculate the junction temperature, when the IC surface temperature is measured. The junction temperature is

$$T_{\rm j} = \Psi_{\rm th(j-top)} \cdot P_d + T_{\rm top}$$

### Table 7Data of reference layout

| Dimensions                             | Material                            | Metal (Copper)                            |

|----------------------------------------|-------------------------------------|-------------------------------------------|

| $76.2\times114.3\times1.5~\text{mm}^3$ | FR4 ( $\lambda_{therm}$ = 0.3 W/mK) | $70\mu m$ ( $\lambda_{therm}$ = 388 W/mK) |

Figure 24 Package outline PG-DSO-14

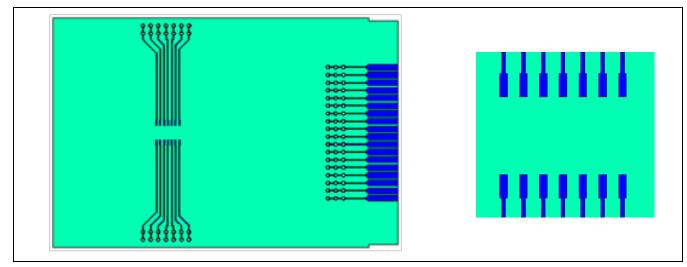

Figure 25 PCB reference layout (according to JEDEC 1s0P) left: Reference layout right: detail of footprint

The thermal coefficient is used to calculate the junction temperature, when the IC surface temperature is measured. The junction temperature is

$$T_{\rm j} = \Psi_{\rm th(j-top)} \cdot P_d + T_{\rm top}$$

### Table 8Data of reference layout

| Dimensions                                  | Material                            | Metal (Copper)                                 |

|---------------------------------------------|-------------------------------------|------------------------------------------------|

| $76.2 \times 114.3 \times 1.5 \text{ mm}^3$ | FR4 ( $\lambda_{therm}$ = 0.3 W/mK) | $70\mu m (\lambda_{therm} = 388 \text{ W/mK})$ |

İnfineon

### 7 Qualification information<sup>1</sup>

#### Table 9Qualification information

| Qualification level        |                      | Industrial <sup>2</sup>                                   |                           |

|----------------------------|----------------------|-----------------------------------------------------------|---------------------------|

|                            |                      | Note: This family of ICs has passed JEDEC's Industrial    |                           |

|                            |                      | qualification. Consumer qualification level is granted by |                           |

|                            |                      | extension of the higher Industrial level.                 |                           |

| Moisture sensitivity level |                      | DSO-8/-14                                                 | MSL3 <sup>3</sup> , 260°C |

|                            |                      |                                                           | (per IPC/JEDEC J-STD-020) |

| ESD                        | Charged device model | Class C3 (> 1.0 kV)                                       |                           |

|                            | Charged device model | (per JESD22-C101)                                         |                           |

|                            |                      | Class 2                                                   |                           |

|                            | Human body model     | (per JEDEC standard JESD22-A114)                          |                           |

| IC latch-up test           |                      | Class II Level A                                          |                           |

|                            |                      | (per JESD85)                                              |                           |

| RoHS compliant             |                      | Yes                                                       |                           |

### 8 Related products

#### Table 10

| Product               | Description                                                                                                               |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------|

| Gate Driver ICs       |                                                                                                                           |

| <u>6EDL04I06 /</u>    | 600 V, 3 phase level shift thin-film SOI gate driver with integrated high speed, low <i>R</i> <sub>DS(ON)</sub> bootstrap |

| 6EDL04N06             | diodes with over-current protection (OCP), 240/420 mA source/sink current drive, Fault reporting,                         |

|                       | and Enable for MOSFET or IGBT switches.                                                                                   |

| 2EDL23I06/            | 600 V, Half-bridge thin-film SOI level shift gate driver with integrated high speed, low                                  |

| 2EDL23N06             | RDSON bootstrap diode, with over-current protection (OCP), 2.3/2.8 A source/sink current driver,                          |

|                       | and one pin Enable/Fault function for MOSFET or IGBT switches.                                                            |

| <b>Power Switches</b> |                                                                                                                           |

| <u>IKD04N60R / RF</u> | 600 V TRENCHSTOP™ IGBT with integrated diode in PG-TO252-3 package                                                        |

| IKD06N65ET6           | 650 V TRENCHSTOP™ IGBT with integrated diode in DPAK                                                                      |

| IPD65R950CFD          | 650 V CoolMOS CFD2 with integrated fast body diode in DPAK                                                                |

| IPN50R950CE           | 500 V CoolMOS CE Superjunction MOSFET in PG-SOT223 package                                                                |

| iMOTION™ Cont         | rollers                                                                                                                   |

| IRMCK099              | iMOTION™ Motor control IC for variable speed drives utilizing sensor-less Field Oriented Control                          |

|                       | (FOC) for Permanent Magnet Synchronous Motors (PMSM).                                                                     |

| <u>IMC101T</u>        | High performance Motor Control IC for variable speed drives based on field oriented control (FOC)                         |

|                       | of permanent magnet synchronous motors (PMSM).                                                                            |

<sup>&</sup>lt;sup>1</sup> Qualification standards can be found at Infineon's web site <u>www.infineon.com</u>

<sup>&</sup>lt;sup>2</sup> Higher qualification ratings may be available should the user have such requirements. Please contact your Infineon sales representative for further information.

<sup>&</sup>lt;sup>3</sup> Higher MSL ratings may be available for the specific package types listed here. Please contact your Infineon sales representative for further information.

## **Revision history**

| <b>Document version</b> | Date of release | Description of changes                                               |  |

|-------------------------|-----------------|----------------------------------------------------------------------|--|

| 0.85                    | 2013-04-16      | Change term VCC in VDD                                               |  |

| 2.6                     | 2016-06-01      | Update maximum Ta from 95°C to 105°C in Table 3                      |  |

| 2.7                     | 2016-08-18      | Updated disclaimer, trademarks. Upated parameter V <sub>HO</sub>     |  |

| 2.8                     | 2018-11-19      | Updated ESD HBM information                                          |  |

| 2.9                     | 2019-01-24      | Updated Chapter 3.8 Tolerant to negative transient voltage on VS pin |  |

|                         |                 |                                                                      |  |

#### Trademarks

All referenced product or service names and trademarks are the property of their respective owners.

Edition 2019-01-24

Published by Infineon Technologies AG 81726 Munich, Germany

© 2019 Infineon Technologies AG. All Rights Reserved.

Do you have a question about this document? Email: erratum@infineon.com

**Document reference**

#### IMPORTANT NOTICE

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics ("Beschaffenheitsgarantie").

With respect to any examples, hints or any typical values stated herein and/or any information regarding the application of the product, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation warranties of non-infringement of intellectual property rights of any third party.

In addition, any information given in this document is subject to customer's compliance with its obligations stated in this document and any applicable legal requirements, norms and standards concerning customer's products and any use of the product of Infineon Technologies in customer's applications.

The data contained in this document is exclusively intended for technically trained staff. It is the responsibility of customer's technical departments to evaluate the suitability of the product for the intended application and the completeness of the product information given in this document with respect to such application. For further information on the product, technology delivery terms and conditions and prices please contact your nearest Infineon Technologies office (www.infineon.com).

Please note that this product is not qualifiec according to the AEC Q100 or AEC Q101 documents of the Automotive Electronics Council.

#### WARNINGS

Due to technical requirements products may contain dangerous substances. For information or the types in question please contact your neares<sup>1</sup> Infineon Technologies office.

Except as otherwise explicitly approved by Infineor Technologies in a written document signed by authorized representatives of Infineor Technologies, Infineon Technologies' products may not be used in any applications where a failure of the product or any consequences of the use thereof car reasonably be expected to result in personal injury.