High Performance 32bit Micro Controller

# **Data Sheet**

V1.0

www.levetop.cn Levetop Electronics Co., Ltd.

# Contents

| 1. | Introduction15                                 |    |  |  |

|----|------------------------------------------------|----|--|--|

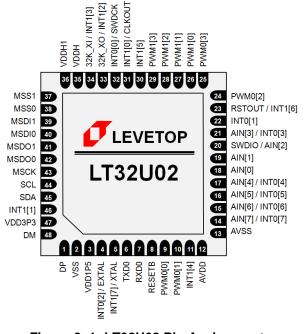

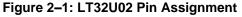

| 2. | Pin Assignment                                 |    |  |  |

| 3. | Features                                       |    |  |  |

| 4. | Block Diagram                                  | 19 |  |  |

| 5. | Signal Properties Summary                      |    |  |  |

| 6. | Signal Descriptions                            | 22 |  |  |

| 7. | Embedded Interrupt Controller                  | 26 |  |  |

|    | 7.1 Introduction                               |    |  |  |

|    | 7.2 Features                                   |    |  |  |

|    | 7.3 Memory Map and Registers                   |    |  |  |

|    | 7.3.1 Memory Map (Base: 0xe000_0000)           |    |  |  |

|    | 7.3.2 Registers                                |    |  |  |

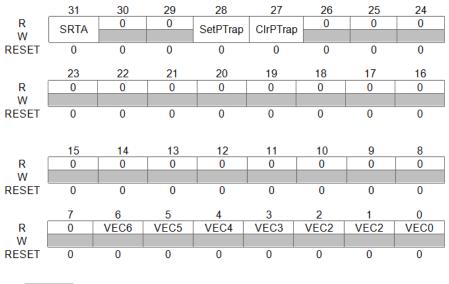

|    | 7.3.2.1 Interrupt Control Status Register      |    |  |  |

|    | 7.3.2.2 Interrupt Enable Register              | 29 |  |  |

|    | 7.3.2.3 Interrupt Pend Set Register            |    |  |  |

|    | 7.3.2.4 Interrupt Pend Clear Register          | 31 |  |  |

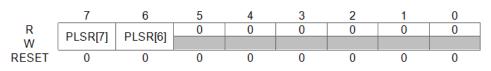

|    | 7.3.2.5 Priority Level Select Registers        |    |  |  |

|    | 7.3.2.6 System Priority Level Select Registers |    |  |  |

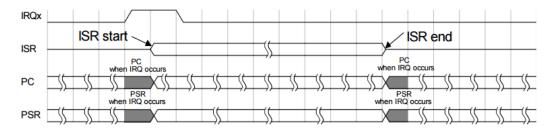

|    | 7.4 Function Description                       |    |  |  |

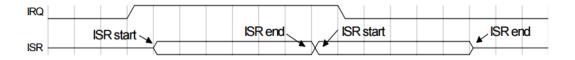

|    | 7.4.1 Interrupt Handling Without Confliction   |    |  |  |

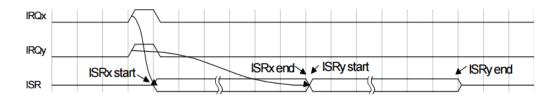

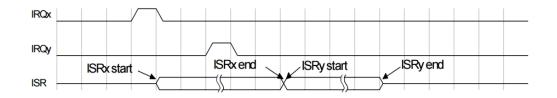

|    | 7.4.2 Interrupt With Confliction               |    |  |  |

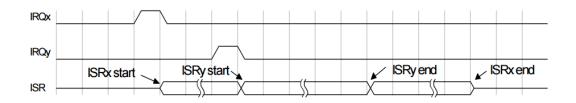

|    | 7.4.3 Pend Trap Function                       |    |  |  |

|    | 7.5 Interrupts                                 |    |  |  |

| 8. | C0 Introduction                                | 38 |  |  |

|    | 8.1 Features                                   |    |  |  |

|    | 8.2 Microarchitecture Summary                  |    |  |  |

|    | 8.3 Programming Model                          |    |  |  |

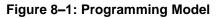

|    | 8.4 Data Format Summary                        | 40 |  |  |

|    | 8.5 Operand Addressing Capabilities            | 40 |  |  |

|    | 8.6 Instruction Set Overview4                  |    |  |  |

# **TLT32U02/32A02**

| 9.  | Embedded Programmable Timer                                   | 43 |  |

|-----|---------------------------------------------------------------|----|--|

|     | 9.1 Introduction                                              |    |  |

|     | 9.2 Memory Map and Registers                                  |    |  |

|     | 9.2.1 Memory Map (Base: 0xe000_1000)                          |    |  |

|     | 9.2.2 Registers                                               |    |  |

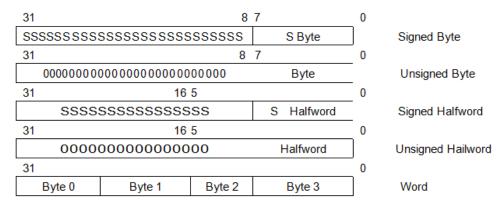

|     | 9.2.2.1 EPT Control Status Register                           |    |  |

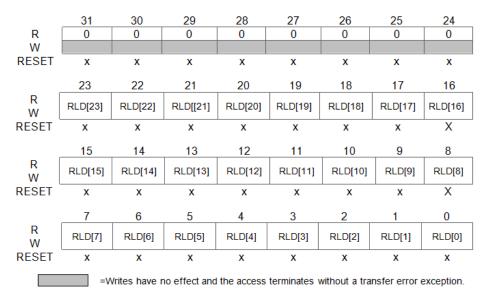

|     | 9.2.2.2 EPT Reload Register                                   |    |  |

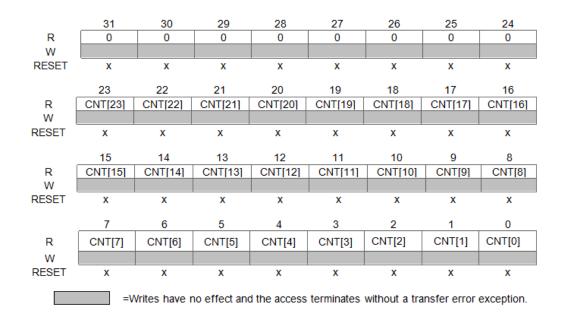

|     | 9.2.2.3 EPT Count Register                                    |    |  |

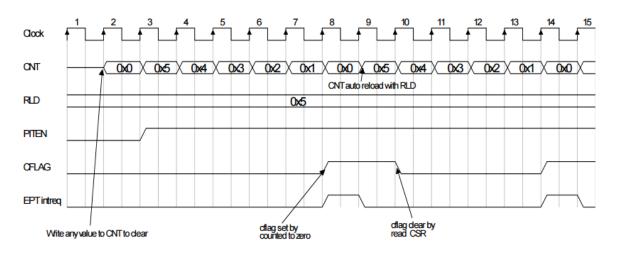

|     | 9.3 Function Description                                      | 47 |  |

|     | 9.3.1 Count Timing                                            |    |  |

| 10. | Chip Configuration Module (CCM)                               | 48 |  |

|     | 10.1 Introduction                                             | 48 |  |

|     | 10.2 Features                                                 | 48 |  |

|     | 10.3 Memory Map and Registers                                 | 48 |  |

|     | 10.3.1 Memory Map (Base: 0x4001_0000)                         |    |  |

|     | 10.3.2 Register Descriptions                                  | 49 |  |

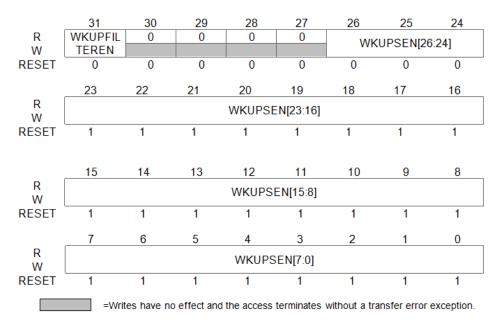

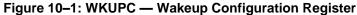

|     | 10.3.2.1 WKUPC — Wakeup Configuration Register                | 49 |  |

|     | 10.3.2.2 CRPDC — Chip Reduce Pin Drive Configuration Register | 51 |  |

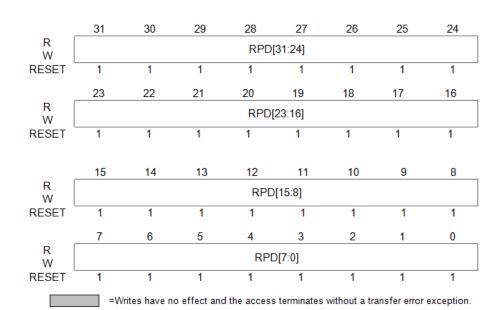

|     | 10.3.2.3 CPSRC — Chip Pin Slow Rate Configuration Register    | 53 |  |

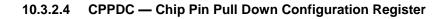

|     | 10.3.2.4 CPPDC — Chip Pin Pull Down Configuration Register    |    |  |

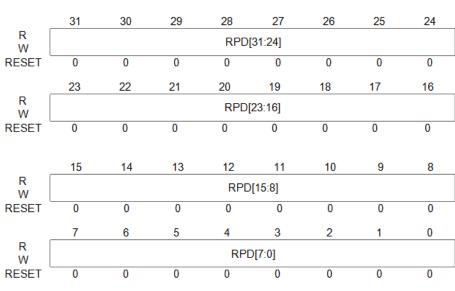

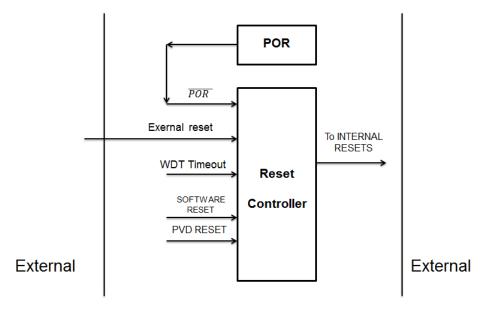

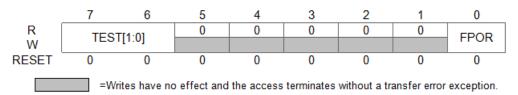

|     | 10.3.2.5 CTR — Chip Test Register                             |    |  |

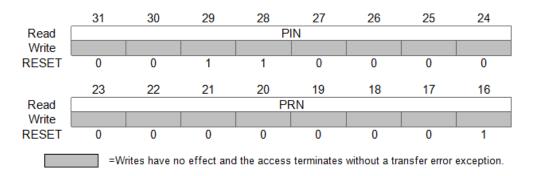

|     | 10.3.2.6 CIR — Chip Identification Register                   |    |  |

| 11. | Clock and Power Control Module                                | 59 |  |

|     | 11.1 Overview                                                 | 59 |  |

|     | 11.2 Features                                                 | 59 |  |

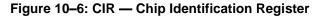

|     | 11.3 Clock Structure                                          | 59 |  |

|     | 11.4 Clock Source Select                                      | 60 |  |

|     | 11.4.1 Low-Power Options                                      |    |  |

|     | 11.4.1.1 Wait and Doze Modes                                  | 60 |  |

|     | 11.4.1.2 Stop Mode                                            | 60 |  |

|     | 11.5 Memory Map and Registers                                 | 61 |  |

|     | 11.5.1 Module Memory Map (Base: 0x4003_0000)                  | 61 |  |

|     | 11.5.2 Register Description                                   | 62 |  |

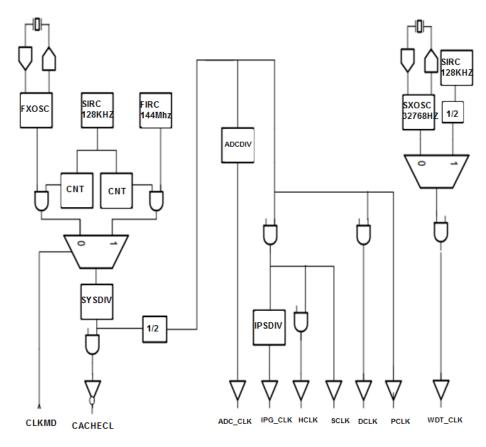

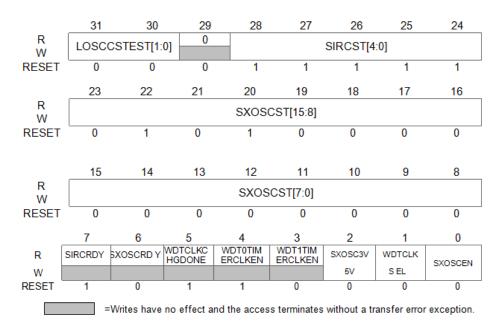

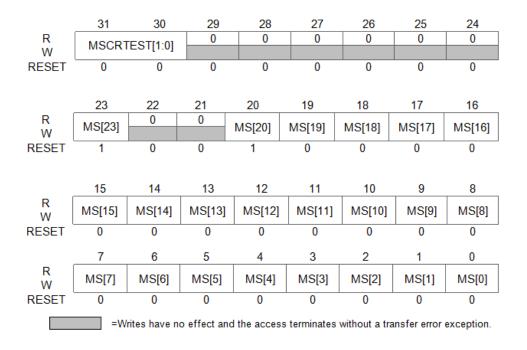

|     | 11.5.2.1 Synthesizer Control Register                         | 62 |  |

|     | 11.5.2.2 Low Speed Oscillator Control and Status Register     | 66 |  |

|     | 11.5.2.3 Module Stop Control Register                         | 68 |  |

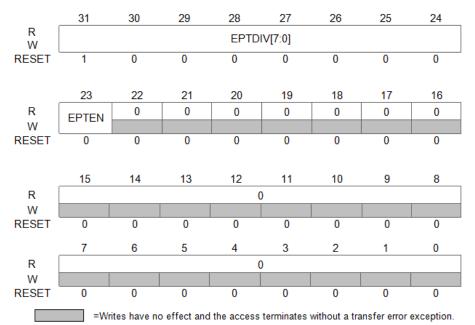

|     | 11.5.2.4 EPT External Clock Source Enable Control Register | 70   |

|-----|------------------------------------------------------------|------|

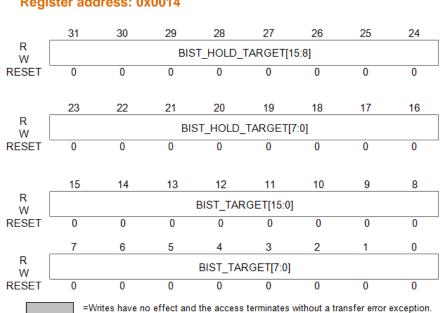

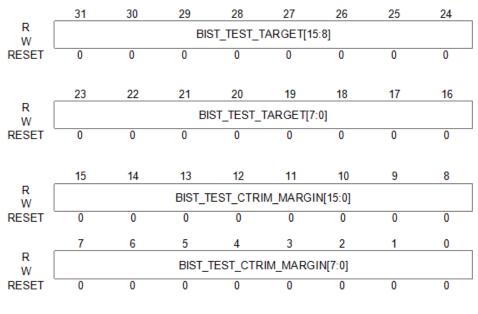

|     | 11.5.2.5 OSC Bist Test Configuration Register1             | 71   |

|     | 11.5.2.6 OSC Bist Test Configuration Register2             | 72   |

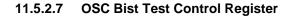

|     | 11.5.2.7 OSC Bist Test Control Register                    | 73   |

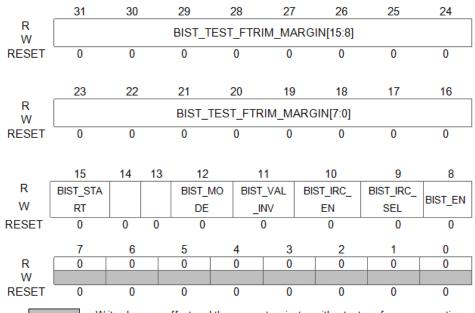

|     | 11.5.2.8 OSC BIST Test Counter Register                    | 74   |

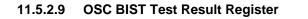

|     | 11.5.2.9 OSC BIST Test Result Register                     | 75   |

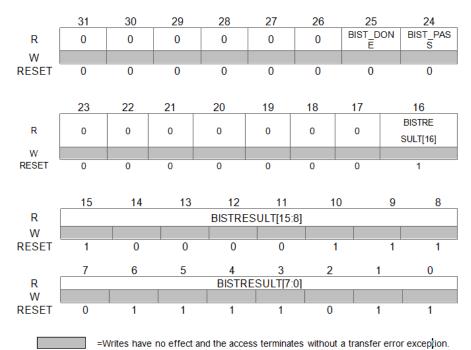

| 12. | Reset Controller Module                                    | .76  |

|     | 12.1 Overview                                              | 76   |

|     | 12.2 Features                                              | . 76 |

|     | 12.3 Block Diagram                                         | . 76 |

|     | 12.4 Memory Map and Registers (Base: 0x4002_0000)          | 77   |

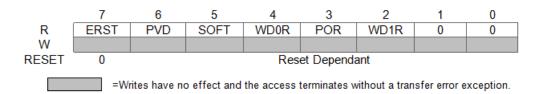

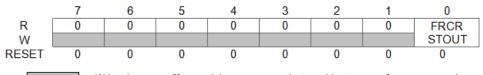

|     | 12.4.1 Reset Test Register                                 | 77   |

|     | 12.4.2 Reset Status Register                               | 78   |

|     | 12.4.3 Reset Control Register                              | 79   |

|     | 12.5 Functional Description                                | . 80 |

|     | 12.5.1 Reset Sources                                       | 80   |

|     | 12.5.1.1 Power-On Reset (POR)                              | 80   |

|     | 12.5.1.2 Watchdog Timer Reset                              |      |

|     | 12.5.1.3 Software Reset                                    |      |

|     | 12.5.1.4 Programmable Voltage Detect Reset                 |      |

|     | 12.5.2 Reset Control Flow                                  | 81   |

| 13. | Static Random Access Memory (SRAM)                         | .82  |

|     | 13.1 Introduction                                          | 82   |

|     | 13.2 Modes of Operation                                    | 82   |

|     | 13.3 Low-Power Modes                                       | 82   |

|     | 13.4 Reset Operation                                       | 82   |

|     | 13.5 Interrupts                                            |      |

|     | •                                                          |      |

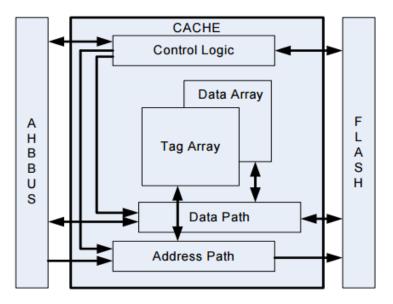

| 14. | Cache (CACHE)                                              | .83  |

|     | 14.1 Features                                              | . 83 |

|     | 14.2 Address Space Model                                   | 83   |

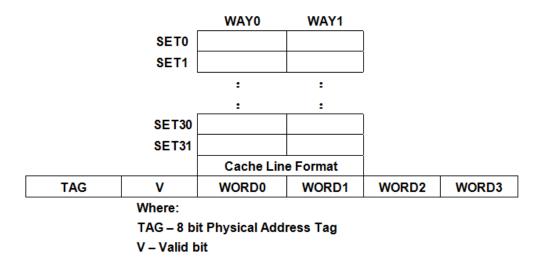

|     | 14.3 Cache Organization                                    | 84   |

|     | 14.4 Cache Operation                                       |      |

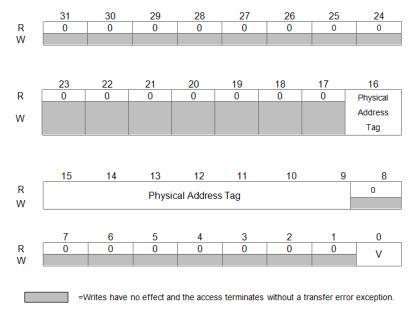

|     | 14.4.1 Cache Line Tag Format                               |      |

|     | 14.4.2 Cache Control                                       |      |

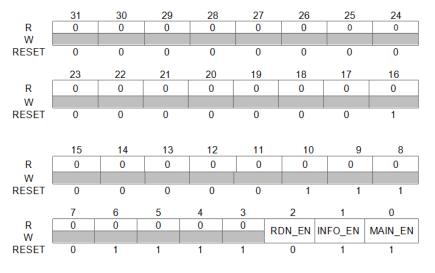

|     | 14.4.2.1 Cache Control Register Format                     |      |

|     |                                                            |      |

|     | 14.4.3 Cache Access Operations                                               | 88    |

|-----|------------------------------------------------------------------------------|-------|

|     | 14.4.3.1 Cache Search                                                        | 88    |

|     | 14.4.3.2 Cache Fill                                                          | 88    |

|     | 14.5 Cache Management                                                        | 88    |

|     | 14.6 Cache Memory Map                                                        | 89    |

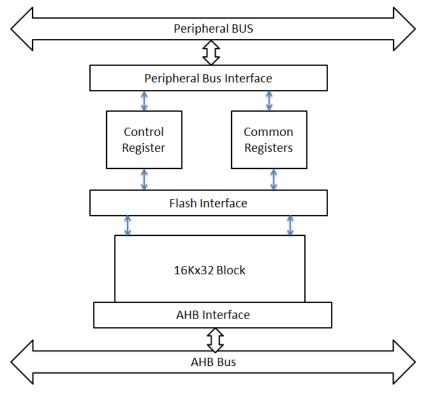

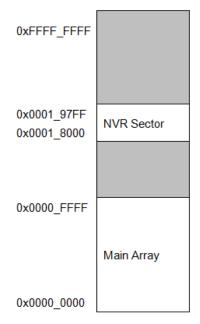

| 15. | Embedded Flash Module                                                        | 91    |

|     | 15.1 Introduction                                                            | 91    |

|     | 15.2 Features                                                                | 91    |

|     | 15.3 Modes of Operation                                                      | 91    |

|     | 15.4 Block Diagram                                                           |       |

|     | 15.5 Module Memory Map (Base: 0x4012_0000)                                   |       |

|     | 15.6 Register Descriptions                                                   |       |

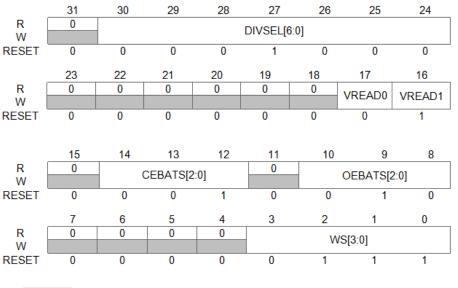

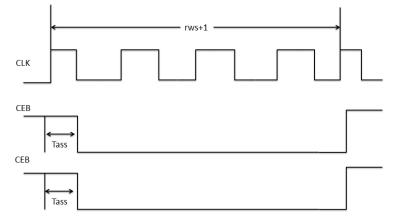

|     | 15.6.1 EFM Configuration Register (EFMCR)                                    |       |

|     | 15.6.2 EFM Security Read Register0 (EFMSEC0)                                 | 96    |

|     | 15.6.3 EFM Security Read Register1 (EFMSEC1)                                 | 97    |

|     | 15.6.4 EFM Security Read Register2 (EFMSEC2)                                 | 98    |

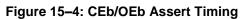

|     | 15.6.5 EFM Timing Register0 (EFMTIM0)                                        |       |

|     | 15.6.6 EFM Timing Register1 (EFMTIM1)                                        |       |

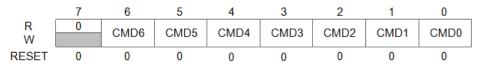

|     | 15.6.7 EFM Command Register (EFMCMD)                                         |       |

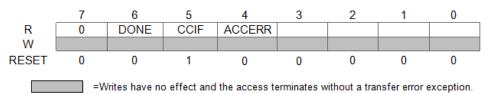

|     | 15.6.8 EFM Status Register (EFMSTAT)                                         |       |

|     | 15.7 Functional Description                                                  | 102   |

|     | 15.7.1 Program and Erase Operations                                          |       |

|     | 15.7.1.1 Setting the EFMTIM0/1 Register                                      |       |

|     | 15.7.1.2 Program, Erase and Verify Sequences                                 |       |

|     | 15.7.1.3 Flash Illegal Operations                                            | 102   |

| 16. | Option Byte                                                                  | . 103 |

|     | 16.1 Register Memory Map (Base: 0x4012_0000)                                 | 103   |

|     | 16.1.1 Register Descriptions                                                 | 103   |

|     | 16.1.1.1 PVDC— Programmable Voltage Detector Configuration Register          | 103   |

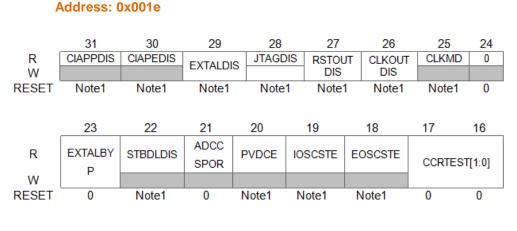

|     | 16.1.1.2 CCR — Customer Configuration Register                               | 105   |

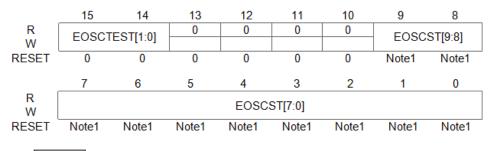

|     | 16.1.1.3 EOSCST— External Oscillator Stable Time Configuration Register      | 108   |

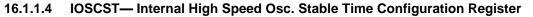

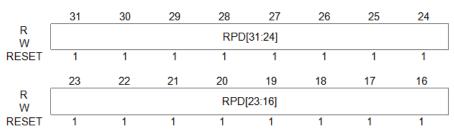

|     | 16.1.1.4 IOSCST— Internal High Speed Osc. Stable Time Configuration Register |       |

|     | 16.1.1.5 RFEVR— RESET Pin Filter Enable and Value Register                   |       |

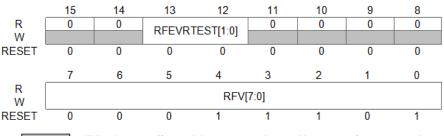

|     | 16.1.1.6 PVDFEVR— Programmable Voltage Detector Filter Control Register      |       |

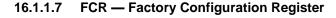

|     | 16.1.1.7 FCR — Factory Configuration Register                                |       |

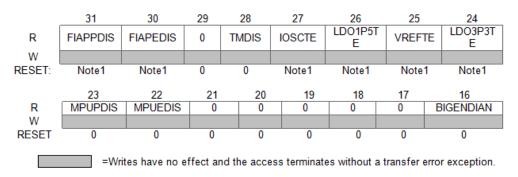

|     | 16.1.1.8 IOSCTC— Internal High Speed Oscillator Trimming Config. Register    |       |

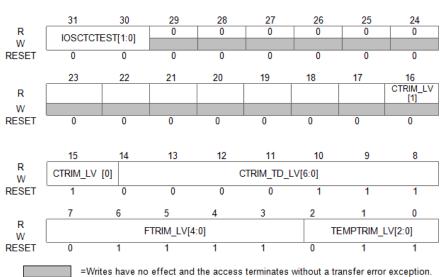

|     | 16.1.1.9 ADCCDISR— ADC Channel Disable Configuration Register                | 114   |

# **TLT32U02/32A02**

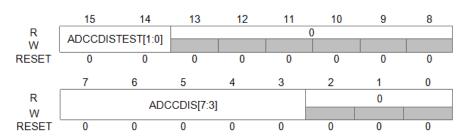

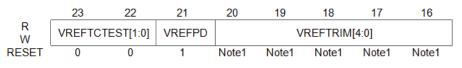

|     | 16.1.1.10 VREFTCR— VREF Trimming Configuration Register                                                                                                                                                                                                                                                                                                                                                                                          | 114                                                                                                                 |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|

|     | 16.1.1.11 LDO1P5TC— LDO1P5 Trimming Configuration Register                                                                                                                                                                                                                                                                                                                                                                                       | 115                                                                                                                 |

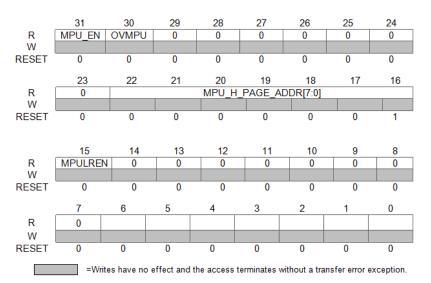

|     | 16.1.1.12 MPUCONFR— Memory Protect Unit Trimming Config. Register                                                                                                                                                                                                                                                                                                                                                                                | 116                                                                                                                 |

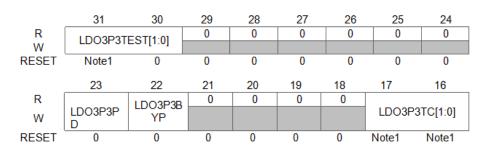

|     | 16.1.1.13 LDO3P3TC— LDO3P3Trimming Configuration Register                                                                                                                                                                                                                                                                                                                                                                                        | 117                                                                                                                 |

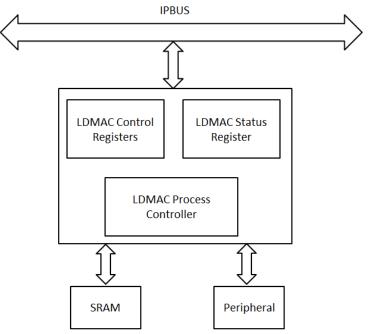

| 17. | LDMA Controller                                                                                                                                                                                                                                                                                                                                                                                                                                  | . 118                                                                                                               |

|     | 17.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                | 118                                                                                                                 |

|     | 17.2 Features                                                                                                                                                                                                                                                                                                                                                                                                                                    | 118                                                                                                                 |

|     | 17.3 Low-Power Mode Operation                                                                                                                                                                                                                                                                                                                                                                                                                    | 118                                                                                                                 |

|     | 17.4 Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                               | 118                                                                                                                 |

|     | 17.5 Module Memory Map (Base: 0x4000_0000)                                                                                                                                                                                                                                                                                                                                                                                                       | 119                                                                                                                 |

|     | 17.6 Register Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                       | 120                                                                                                                 |

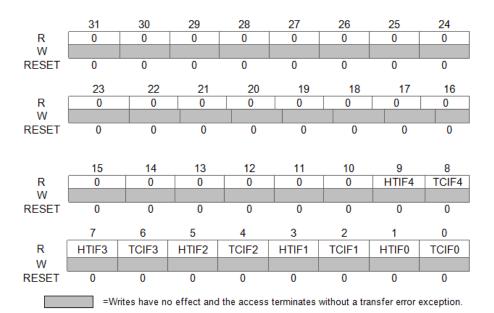

|     | 17.6.1 LDMA Status Register (LDMASR)                                                                                                                                                                                                                                                                                                                                                                                                             | 120                                                                                                                 |

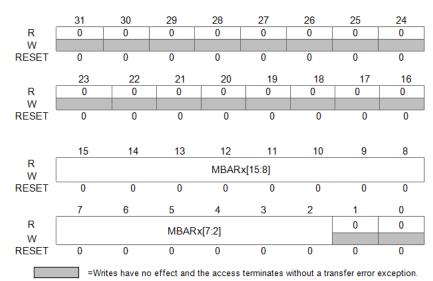

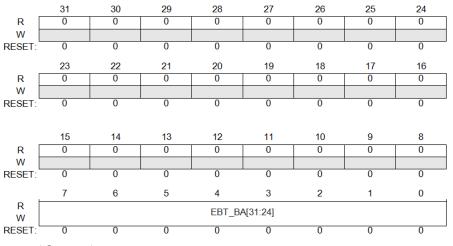

|     | 17.6.2 LDMA Memory Base Address Register (LDMAMBARx)                                                                                                                                                                                                                                                                                                                                                                                             | 121                                                                                                                 |

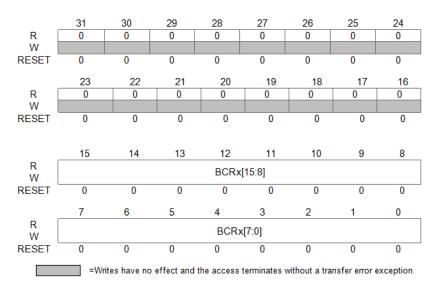

|     | 17.6.3 LDMA Byte Count Register (LDMABCRx)                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                     |

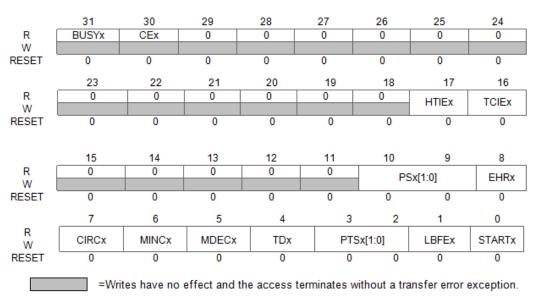

|     | 17.6.4 LDMA Control Register (LDMACRx)                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                     |

|     | 17.7 Function Description                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                     |

|     | 17.7.1 Circular Mode                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                     |

|     | 17.7.2 Channel Configuration Procedure                                                                                                                                                                                                                                                                                                                                                                                                           | 125                                                                                                                 |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                     |

| 18. | Programmable Interrupt Timer Modules (PIT)                                                                                                                                                                                                                                                                                                                                                                                                       | . 126                                                                                                               |

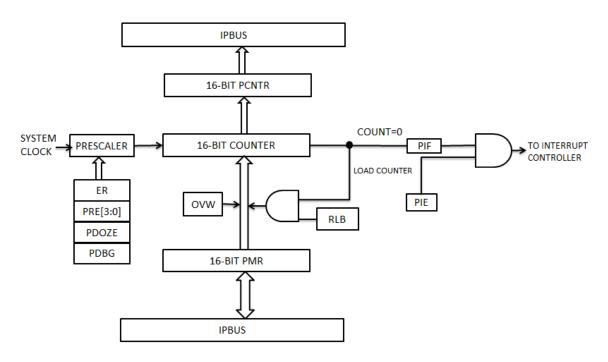

| 18. | Programmable Interrupt Timer Modules (PIT)<br>18.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                     |

| 18. |                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 126                                                                                                                 |

| 18. | 18.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                | 126<br>126                                                                                                          |

| 18. | 18.1 Introduction         18.2 Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                     | 126<br>126<br>127                                                                                                   |

| 18. | <ul> <li>18.1 Introduction</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                             | 126<br>126<br>127<br>127                                                                                            |

| 18. | <ul> <li>18.1 Introduction</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                             | 126<br>126<br>127<br>127<br>127                                                                                     |

| 18. | <ul> <li>18.1 Introduction</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                             | 126<br>126<br>127<br>127<br>127<br>127                                                                              |

| 18. | <ul> <li>18.1 Introduction</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                             | 126<br>126<br>127<br>127<br>127<br>127<br>127<br>127                                                                |

| 18. | <ul> <li>18.1 Introduction</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                             | 126<br>126<br>127<br>127<br>127<br>127<br>127<br>127                                                                |

| 18. | <ul> <li>18.1 Introduction</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                             | 126<br>126<br>127<br>127<br>127<br>127<br>127<br>127<br>127                                                         |

| 18. | <ul> <li>18.1 Introduction</li> <li>18.2 Block Diagram</li> <li>18.3 Modes of Operation</li> <li>18.3.1 Wait Mode</li> <li>18.3.2 Doze Mode</li> <li>18.3.3 Stop Mode</li> <li>18.3.4 Debug Mode</li> <li>18.4 Signals</li> <li>18.5 Memory Map and Registers</li> <li>18.5.1 Memory Map</li> <li>18.5.2 Registers</li> </ul>                                                                                                                    | 126<br>126<br>127<br>127<br>127<br>127<br>127<br>128<br>128<br>128                                                  |

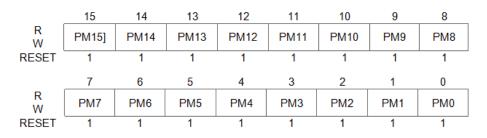

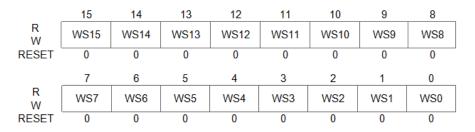

| 18. | <ul> <li>18.1 Introduction</li> <li>18.2 Block Diagram</li> <li>18.3 Modes of Operation</li> <li>18.3.1 Wait Mode</li> <li>18.3.2 Doze Mode</li> <li>18.3.3 Stop Mode</li> <li>18.3.4 Debug Mode</li> <li>18.4 Signals</li> <li>18.5 Memory Map and Registers</li> <li>18.5.1 Memory Map</li> <li>18.5.2 Registers</li> <li>18.5.2 Registers</li> <li>18.5.2.1 PIT Modulus Register</li> </ul>                                                   | 126<br>126<br>127<br>127<br>127<br>127<br>127<br>127<br>128<br>128<br>128<br>128                                    |

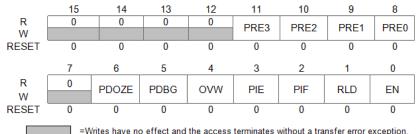

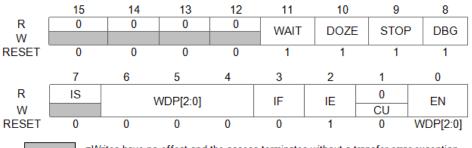

| 18. | <ul> <li>18.1 Introduction</li> <li>18.2 Block Diagram</li> <li>18.3 Modes of Operation</li> <li>18.3.1 Wait Mode</li> <li>18.3.2 Doze Mode</li> <li>18.3.3 Stop Mode</li> <li>18.3.4 Debug Mode</li> <li>18.4 Signals</li> <li>18.5 Memory Map and Registers</li> <li>18.5.1 Memory Map</li> <li>18.5.2 Registers</li> <li>18.5.2 Registers</li> <li>18.5.2.1 PIT Modulus Register</li> <li>18.5.2.2 PIT Control and Status Register</li> </ul> | 126<br>127<br>127<br>127<br>127<br>127<br>127<br>127<br>128<br>128<br>128<br>128<br>128                             |

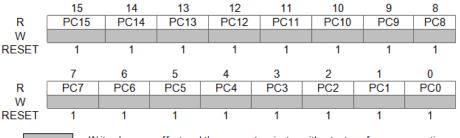

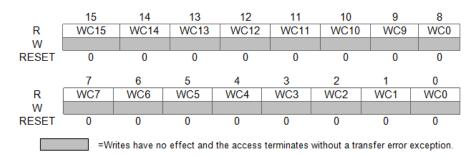

| 18. | <ul> <li>18.1 Introduction</li> <li>18.2 Block Diagram</li> <li>18.3 Modes of Operation</li> <li>18.3.1 Wait Mode</li> <li>18.3.2 Doze Mode</li> <li>18.3.3 Stop Mode</li> <li>18.3.4 Debug Mode</li> <li>18.4 Signals</li> <li>18.5 Memory Map and Registers</li> <li>18.5.1 Memory Map</li> <li>18.5.2 Registers</li> <li>18.5.2.2 PIT Control and Status Register</li> <li>18.5.2.3 PIT Count Register</li> </ul>                             | 126<br>127<br>127<br>127<br>127<br>127<br>127<br>127<br>128<br>128<br>128<br>128<br>128<br>129<br>131               |

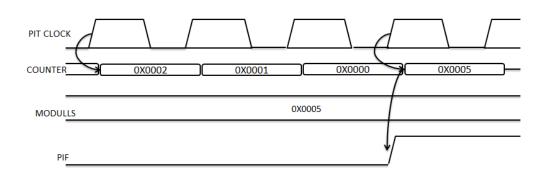

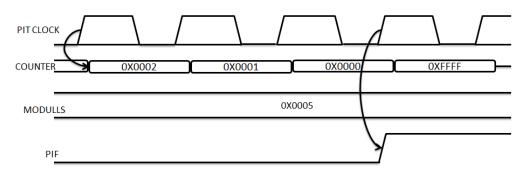

| 18. | <ul> <li>18.1 Introduction</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                             | 126<br>127<br>127<br>127<br>127<br>127<br>127<br>127<br>128<br>128<br>128<br>128<br>128<br>129<br>131<br>132        |

| 18. | <ul> <li>18.1 Introduction</li> <li>18.2 Block Diagram</li> <li>18.3 Modes of Operation</li> <li>18.3.1 Wait Mode</li> <li>18.3.2 Doze Mode</li> <li>18.3.3 Stop Mode</li> <li>18.3.4 Debug Mode</li> <li>18.4 Signals</li> <li>18.5 Memory Map and Registers</li> <li>18.5.1 Memory Map</li> <li>18.5.2 Registers</li> <li>18.5.2.2 PIT Control and Status Register</li> <li>18.5.2.3 PIT Count Register</li> </ul>                             | 126<br>127<br>127<br>127<br>127<br>127<br>127<br>127<br>127<br>128<br>128<br>128<br>128<br>128<br>131<br>132<br>132 |

|     | 18.6.3 Timeout Specifications                                             | 133                                                                                                          |

|-----|---------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

|     | 18.7 Interrupt Operation                                                  | 133                                                                                                          |

| 19. | Watchdog Timer Module                                                     | 134                                                                                                          |

|     | 19.1 Introduction                                                         | 134                                                                                                          |

|     | 19.2 Modes of Operation                                                   | 134                                                                                                          |

|     | 19.2.1 Wait Mode                                                          | 134                                                                                                          |

|     | 19.2.2 Doze Mode                                                          | 134                                                                                                          |

|     | 19.2.3 Stop Mode                                                          | 134                                                                                                          |

|     | 19.2.4 Debug Mode                                                         | 134                                                                                                          |

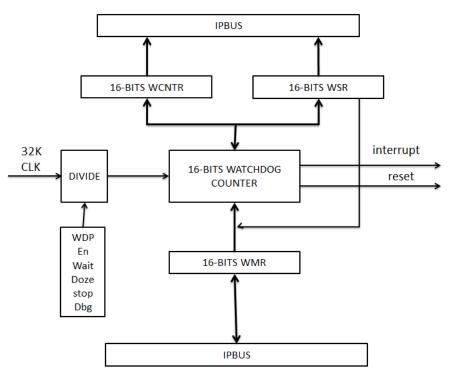

|     | 19.3 Block Diagram                                                        | 135                                                                                                          |

|     | 19.4 Signals                                                              | 135                                                                                                          |

|     | 19.5 Memory Map and Registers                                             | 136                                                                                                          |

|     | 19.5.1 Memory Map (Base: 0x4013_0000, 0x4014_0000)                        | 136                                                                                                          |

|     | 19.5.2 Registers                                                          | 136                                                                                                          |

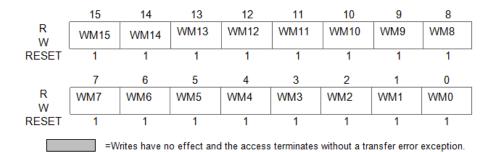

|     | 19.5.2.1 Watchdog Modules Register                                        | 137                                                                                                          |

|     | 19.5.2.2 Watchdog Control Register                                        | 137                                                                                                          |

|     | 19.5.2.3 Watchdog Service Register                                        |                                                                                                              |

|     | 19.5.2.4 Watchdog Count Register                                          | 139                                                                                                          |

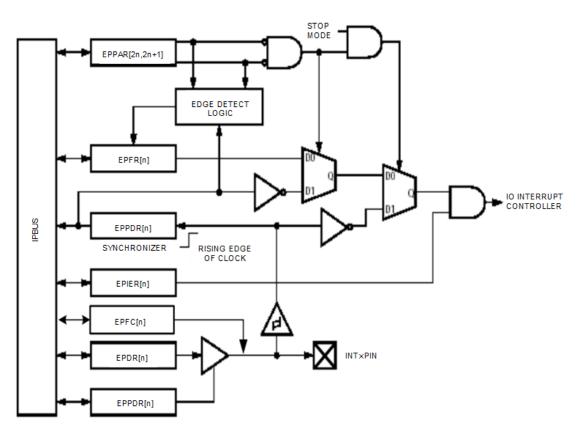

| 20. | Edge Port Module (EPORT)                                                  | 140                                                                                                          |

|     |                                                                           |                                                                                                              |

|     | 20.1 Introduction                                                         |                                                                                                              |

|     | <ul><li>20.1 Introduction</li><li>20.2 Low-Power Mode Operation</li></ul> | 140                                                                                                          |

|     |                                                                           | 140<br>141                                                                                                   |

|     | 20.2 Low-Power Mode Operation                                             | 140<br>141<br>141                                                                                            |

|     | 20.2 Low-Power Mode Operation<br>20.2.1 Wait and Doze Modes               | 140<br>141<br>141<br>141                                                                                     |

|     | 20.2 Low-Power Mode Operation<br>20.2.1 Wait and Doze Modes               | 140<br>141<br>141<br>141<br>141                                                                              |

|     | <ul> <li>20.2 Low-Power Mode Operation</li></ul>                          | 140<br>141<br>141<br>141<br>141<br>142                                                                       |

|     | <ul> <li>20.2 Low-Power Mode Operation</li></ul>                          | 140<br>141<br>141<br>141<br>141<br>142<br>142                                                                |

|     | <ul> <li>20.2 Low-Power Mode Operation</li></ul>                          | 140<br>141<br>141<br>141<br>141<br>142<br>142<br>142<br>142                                                  |

|     | <ul> <li>20.2 Low-Power Mode Operation</li></ul>                          | 140<br>141<br>141<br>141<br>141<br>142<br>142<br>142<br>142<br>                                              |

|     | <ul> <li>20.2 Low-Power Mode Operation</li></ul>                          | 140<br>141<br>141<br>141<br>141<br>141<br>142<br>142<br>142<br>143<br>143<br>143<br>144                      |

|     | <ul> <li>20.2 Low-Power Mode Operation</li></ul>                          | 140<br>141<br>141<br>141<br>141<br>142<br>142<br>142<br>142<br>143<br>143<br>144<br>145                      |

|     | <ul> <li>20.2 Low-Power Mode Operation</li></ul>                          | 140<br>141<br>141<br>141<br>141<br>141<br>142<br>142<br>142<br>143<br>143<br>145<br>145                      |

|     | <ul> <li>20.2 Low-Power Mode Operation</li></ul>                          | 140<br>141<br>141<br>141<br>141<br>142<br>142<br>142<br>142<br>143<br>143<br>144<br>145<br>145<br>146        |

|     | <ul> <li>20.2 Low-Power Mode Operation</li></ul>                          | 140<br>141<br>141<br>141<br>141<br>142<br>142<br>142<br>143<br>143<br>145<br>145<br>146<br>146               |

|     | <ul> <li>20.2 Low-Power Mode Operation</li></ul>                          | 140<br>141<br>141<br>141<br>141<br>141<br>142<br>142<br>142<br>143<br>143<br>145<br>145<br>146<br>147        |

|     | <ul> <li>20.2 Low-Power Mode Operation</li></ul>                          | 140<br>141<br>141<br>141<br>141<br>142<br>142<br>142<br>142<br>143<br>143<br>145<br>145<br>146<br>147<br>147 |

|     | 20.4.2.11 EPORT Level Polarity Register                                            |     |

|-----|------------------------------------------------------------------------------------|-----|

|     | 20.4.2.12 EPORT Port Bit Clear Register                                            | 148 |

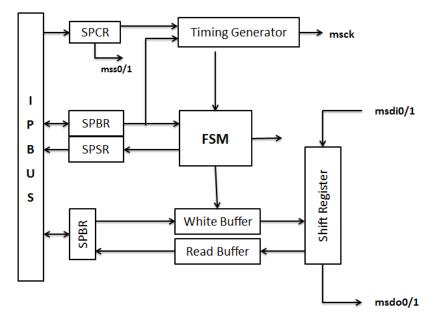

| 21. | Sensor Controller Module (SCM)                                                     | 149 |

|     | 21.1 Overview                                                                      | 149 |

|     | 21.2 Features                                                                      | 149 |

|     | 21.3 Block Diagram                                                                 | 149 |

|     | 21.4 Signal Description                                                            | 150 |

|     | 21.5 Memory Map and Registers (Base: 0x400c_0000)                                  | 150 |

|     | 21.5.1 Register Description                                                        |     |

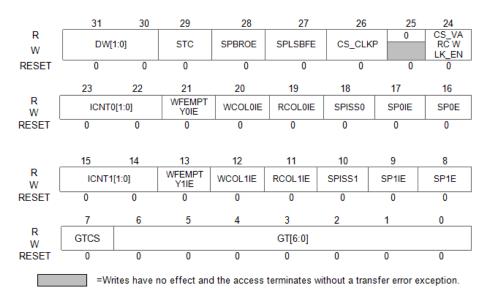

|     | 21.5.1.1 SCM Control Register                                                      |     |

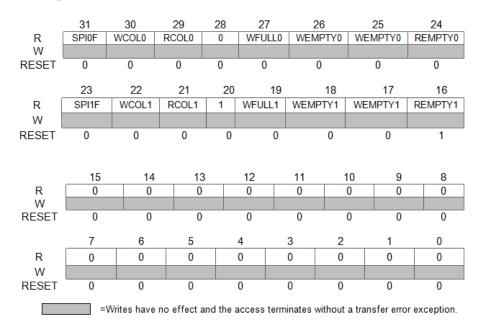

|     | 21.5.1.2 SCM Status Register                                                       |     |

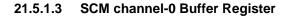

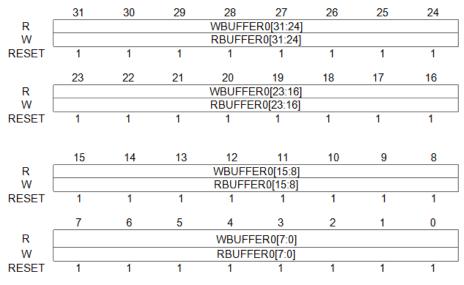

|     | 21.5.1.3 SCM channel-0 Buffer Register                                             |     |

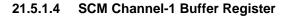

|     | 21.5.1.4 SCM Channel-1 Buffer Register                                             |     |

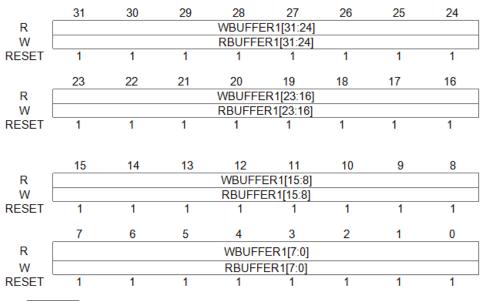

|     | 21.5.1.5 SCM Baud Rate Register                                                    |     |

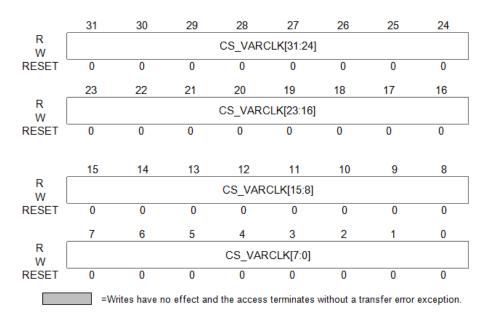

|     | 21.5.1.6 SCM Bit Period Select Register                                            |     |

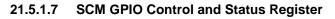

|     | 21.5.1.7 SCM GPIO Control and Status Register<br>21.5.1.8 SCM DMA Control Register |     |

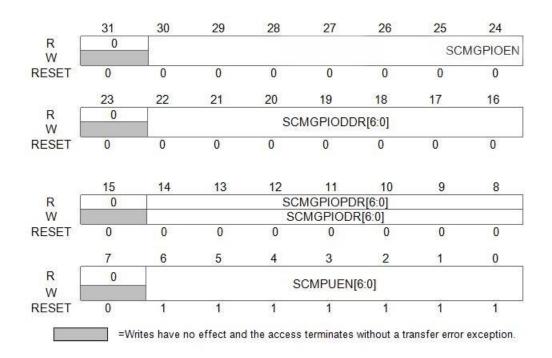

|     | 21.5.1.6 SCM DMA Control Register                                                  |     |

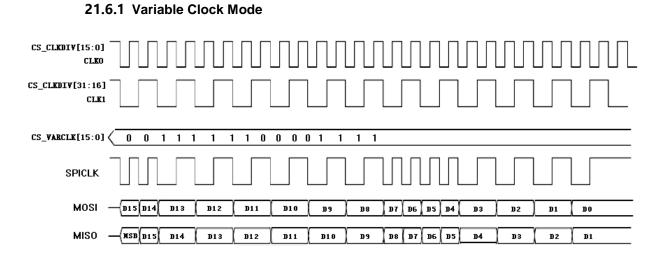

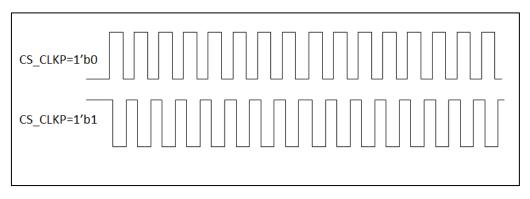

|     | 21.6 Operation<br>21.6.1 Variable Clock Mode                                       |     |

|     | 21.6.1 Variable Clock Mode                                                         |     |

|     | 21.6.3 Serial Communication                                                        |     |

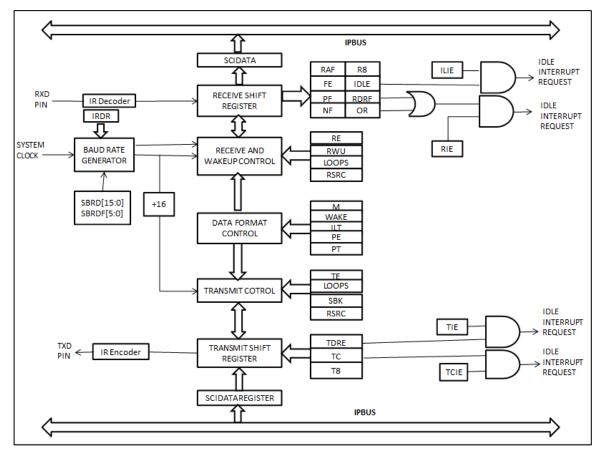

| 22. | Serial Communications Interface Module (SCI)                                       |     |

|     | 22.1 Introduction                                                                  |     |

|     | 22.2 Features                                                                      |     |

|     | 22.3 Modes of Operation                                                            |     |

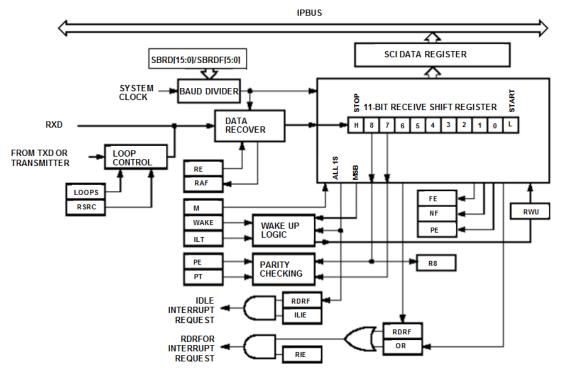

|     | 22.4 Block Diagram                                                                 |     |

|     | 22.5 Modes of Operation                                                            |     |

|     | 22.5.1 Doze Mode                                                                   |     |

|     | 22.5.2 Stop Mode                                                                   |     |

|     | 22.6 Signal Description                                                            |     |

|     | 22.6.1 RXD                                                                         |     |

|     | 22.6.2 TXD                                                                         |     |

|     | 22.7 Memory Map and Registers (Base: 0x4009 0000)                                  |     |

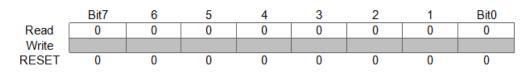

|     | 22.7.1 SCI Control Register 2                                                      |     |

|     | 22.7.2 SCI Control Register 1                                                      |     |

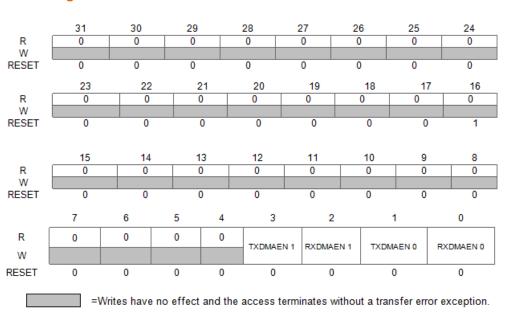

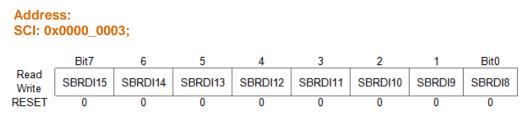

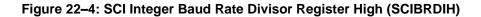

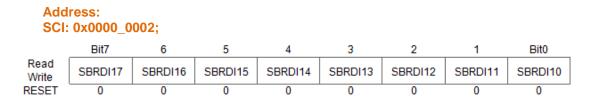

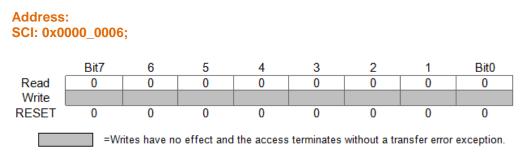

|     | 22.7.3 SCI Baud Rate Divisor Registers                                             |     |

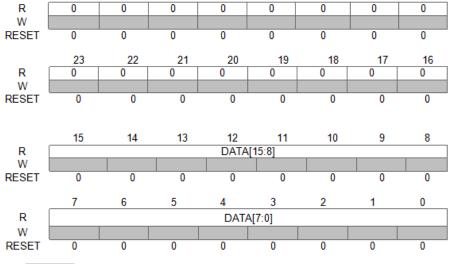

| 22.7.4 SCI I                                 | ata Registers                |                    |  |  |

|----------------------------------------------|------------------------------|--------------------|--|--|

| 22.7.5 SCI 9                                 | 22.7.5 SCI Status Register 2 |                    |  |  |

| 22.7.6 SCI S                                 |                              |                    |  |  |

| 22.7.7 SCI I                                 |                              |                    |  |  |

| 22.7.8 SCI I                                 |                              |                    |  |  |

| 22.7.9 SCI Pullup and Reduced Drive Register |                              |                    |  |  |

| 22.7.10                                      | SCI InfraRed Divisor Regis   | ter                |  |  |

| 22.7.11                                      | SCI InfraRed Control Regi    | ster 181           |  |  |

| 22.7.12                                      | -                            |                    |  |  |

| 22.8 Functio                                 | al Description               |                    |  |  |

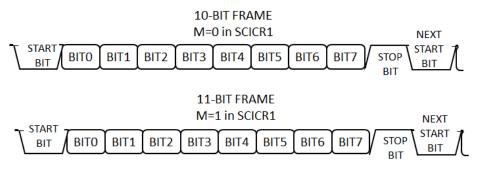

| 22.9 Data Fo                                 | rmat                         |                    |  |  |

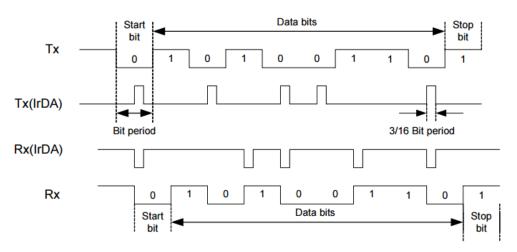

| 22.10Serial IF                               | (SIR)                        |                    |  |  |

| 22.11 Baud Ra                                | te Generation                |                    |  |  |

| 22.12Transm                                  | tter                         |                    |  |  |

| 22.12.1                                      | Frame Length                 |                    |  |  |

| 22.12.2                                      | Transmitting A Frame         |                    |  |  |

| 22.12.3                                      | Break Frames                 |                    |  |  |

| 22.12.4                                      | Idle Frames                  |                    |  |  |

| 22.13Receive                                 |                              |                    |  |  |

| 22.13.1                                      | Frame Length                 |                    |  |  |

| 22.13.2                                      | Receiving A Frame            |                    |  |  |

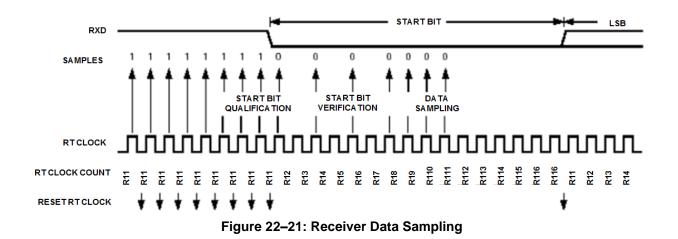

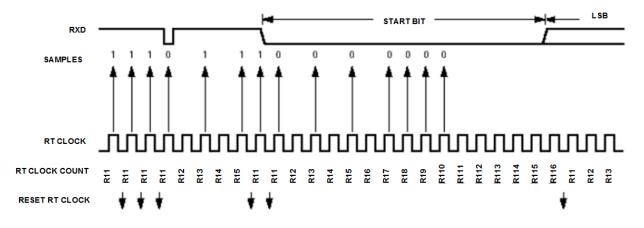

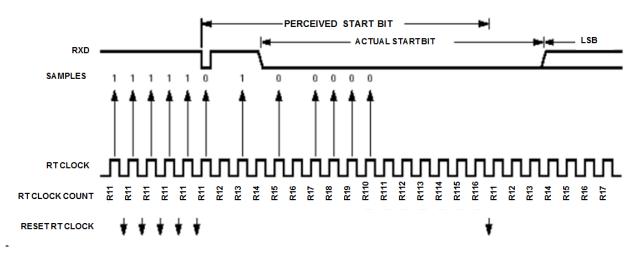

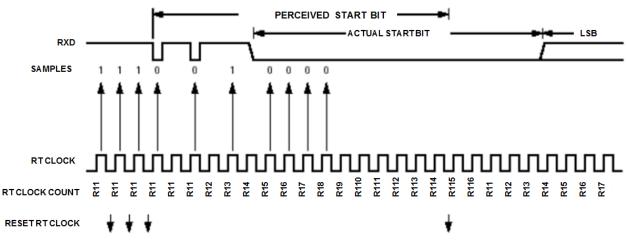

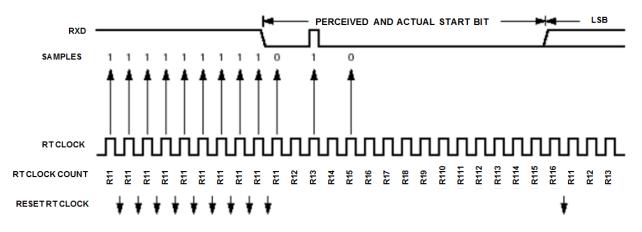

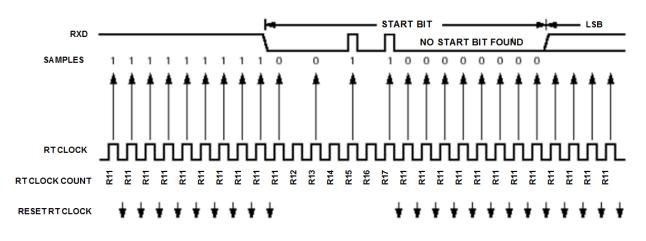

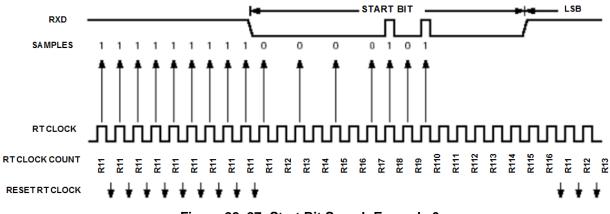

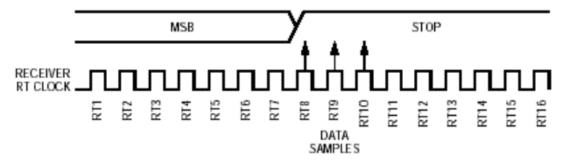

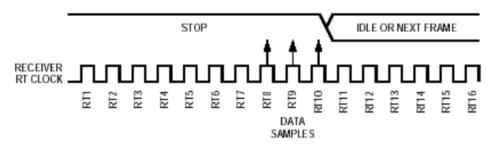

| 22.13.3                                      | Data Sampling                |                    |  |  |

| 22.13.4                                      | Framing Errors               |                    |  |  |

| 22.13.5                                      |                              |                    |  |  |

| 22.1                                         | .5.1 Slow Data Toleran       | ce 196             |  |  |

| 22.1                                         | .5.2 Fast Data Tolerand      | e                  |  |  |

| 22.13.6                                      | •                            |                    |  |  |

| 22.1                                         | •                            | keup (WAKE = 0)198 |  |  |

| 22.1                                         | .6.2 Address Mark Wal        | xeup (WAKE = 1)    |  |  |

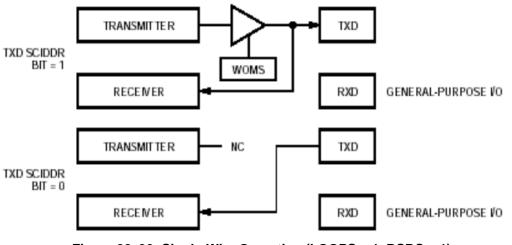

| 22.14Single-                                 | Vire Operation               |                    |  |  |

| 22.15Loop O                                  | peration                     |                    |  |  |

| 22.16I/O Por                                 | S                            |                    |  |  |

| 22.17Reset                                   |                              |                    |  |  |

| 22.18Interrup                                | ts                           |                    |  |  |

| 22.18.1                                      | Transmit Data Register Er    | 101 npty           |  |  |

| 22.18.2                                      | Transmission Complete        |                    |  |  |

| 22.18.3                                      | Receive Data Register Ful    |                    |  |  |

| 22.18.4                                      | Idle Receiver Input          |                    |  |  |

# *T***LT32U02/32A02**

|     | 22.18.5 Overrun                                      |     |

|-----|------------------------------------------------------|-----|

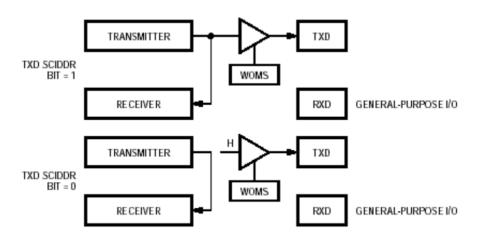

| 23. | USB2.0 Full-Speed Device Controller                  |     |

|     | 23.1 Introduction                                    |     |

|     | 23.2 Features                                        |     |

|     | 23.3 Block Diagram                                   |     |

|     | 23.4 Modes of Operation                              |     |

|     | 23.4.1 Wait Mode                                     |     |

|     | 23.4.2 Doze Mode                                     |     |

|     | 23.4.3 Stop Mode                                     |     |

|     | 23.5 Memory Map and Registers                        |     |

|     | 23.5.1 Memory Map                                    |     |

|     | 23.5.2 Registers                                     |     |

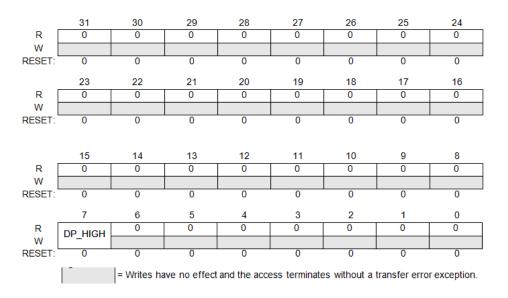

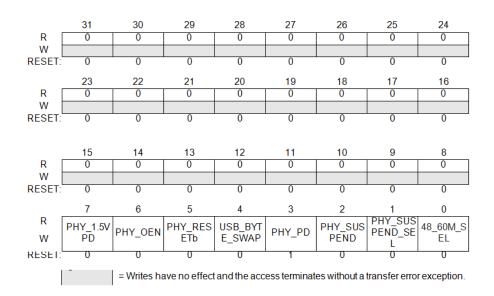

|     | 23.5.2.1 USBPHY Control Register 1 (USBPHY CTRL1)    |     |

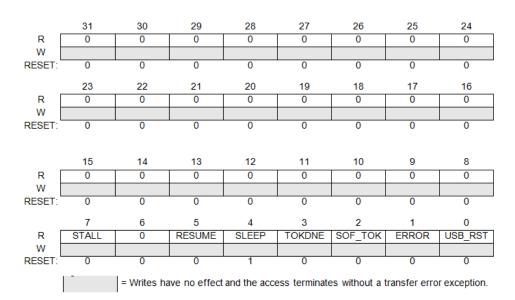

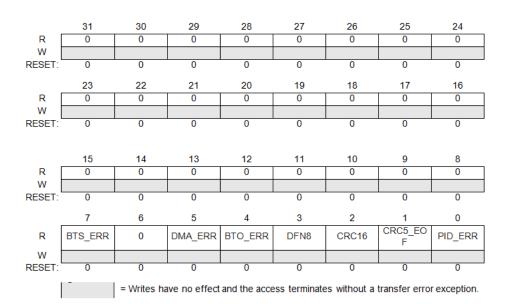

|     | 23.5.2.2 Interrupt Status Register (INT_STAT)        |     |

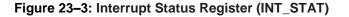

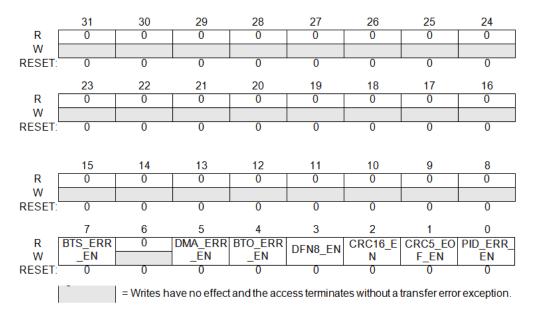

|     | 23.5.2.3 Interrupt Enable Register (INT_ENB)         |     |

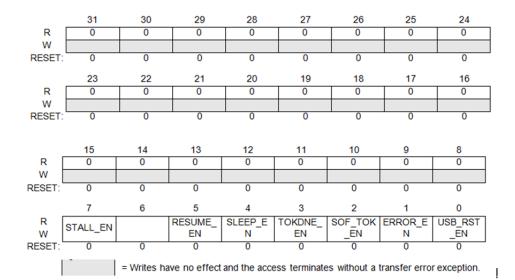

|     | 23.5.2.4 Error Interrupt Status Register (ERR_STAT)  |     |

|     | 23.5.2.5 Error Interrupt Enable Register (ERR_ENB)   |     |

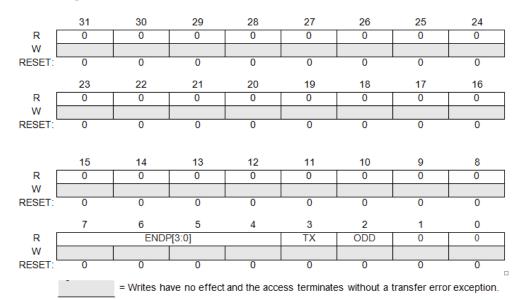

|     | 23.5.2.6 Status Register (STAT)                      |     |

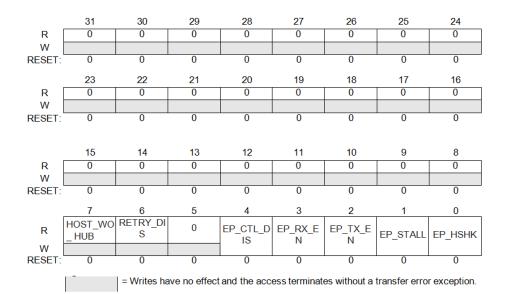

|     | 23.5.2.7 Control Register (CTL)                      |     |

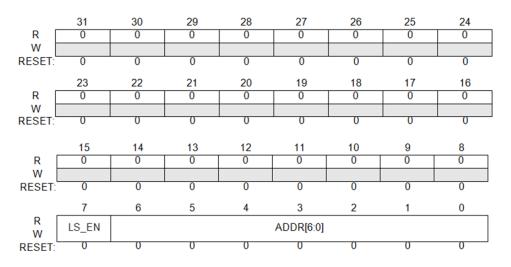

|     | 23.5.2.8 Address Register (ADDR)                     |     |

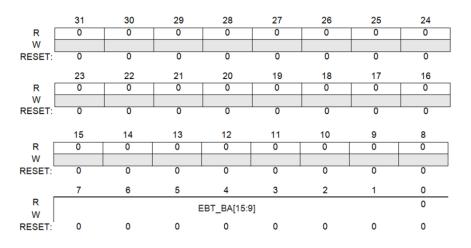

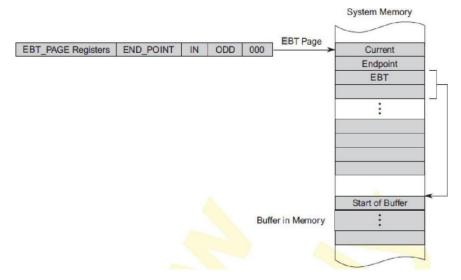

|     | 23.5.2.9 EBT Page Register 1 (EBT_PAGE_01)           |     |

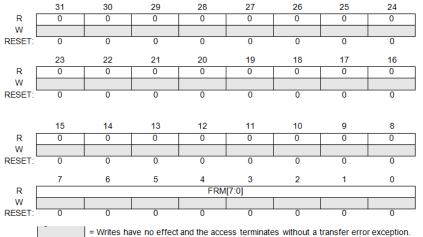

|     | 23.5.2.10 Frame Number Register (FRMNUML)            |     |

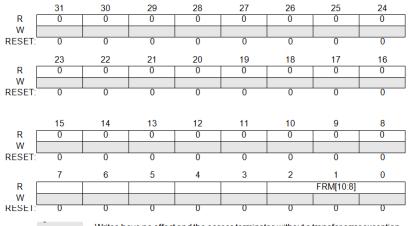

|     | 23.5.2.11 Frame Number Register (FRMNUMH)            |     |

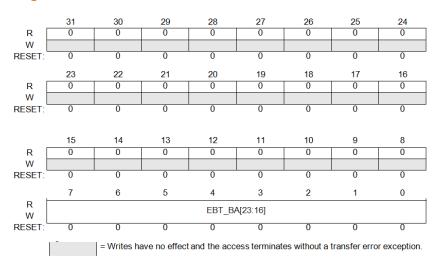

|     | 23.5.2.12 EBT Page Register 2 (EBT_PAGE_02)          |     |

|     | 23.5.2.13 EBT Page Register 3 (EBT_PAGE_03)          |     |

|     | 23.5.2.14 Endpoint Control Registers (ENDPTn, n=0-7) |     |

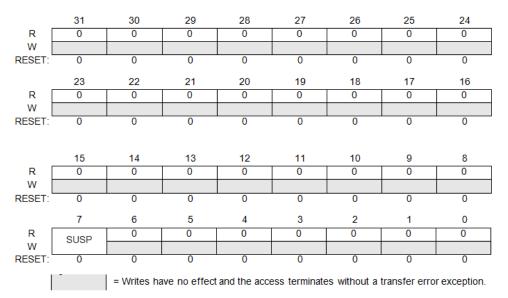

|     | 23.5.2.15 USB Resume Enable Register (USB_RESMEN)    |     |

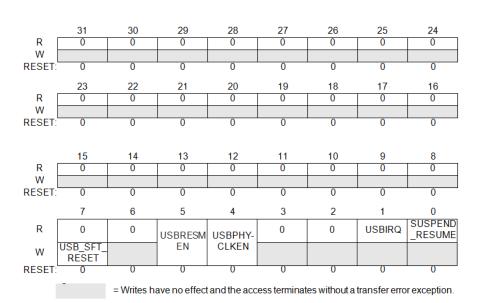

|     | 23.5.2.16 USB PHY Control Register3 (USBPHY_CTRL3)   |     |

|     | 23.6 Function Description                            | 223 |

|     | 23.6.1 Data Structure                                |     |

|     | 23.6.2 Endpoint Buffer Table                         |     |

|     | 23.6.3 Rx vs. Tx as a USB Target Device              |     |

|     | 23.6.4 Addressing Endpoint Buffer Table Entries      |     |

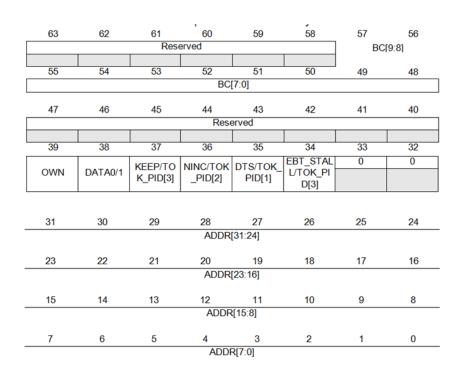

|     | 23.6.5 Endpoint Buffer Table Formats                 |     |

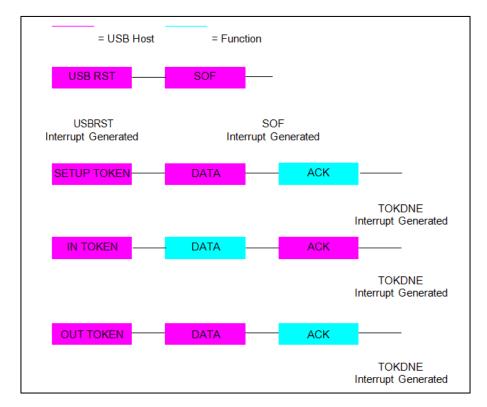

|     | 23.6.6 USB Transaction                               |     |

| 24. | I2C                                                  | 229 |

|     | 24.1 Introduction                                    | 229 |

# **TLT32U02/32A02**

| 24.2 Features                                                 | 229 |

|---------------------------------------------------------------|-----|

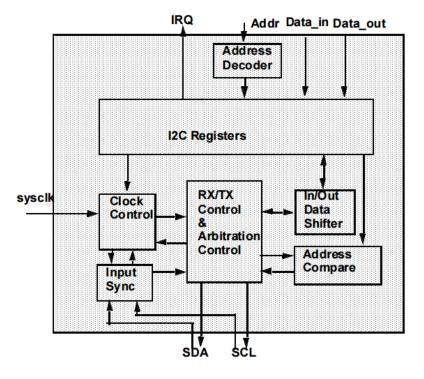

| 24.3 System and Block Diagram                                 | 230 |

| 24.4 Memory Map and Registers (Base: 0x4015_0000)             |     |

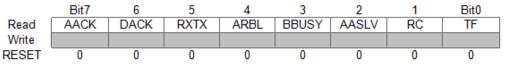

| 24.4.1 I2C Status Register (I2CS)                             |     |

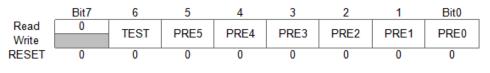

| 24.4.2 I2C Clock Prescalar Register (I2CP)                    |     |

| 24.4.3 I2C Control Register (I2CC)                            |     |

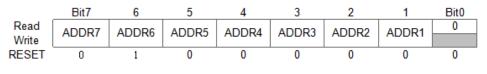

| 24.4.4 I2C Slave Address Register (I2CSA)                     |     |

| 24.4.5 I2C Port Control Register (I2CPCR)                     |     |

| 24.4.6 I2C Slave High-Speed Mode Indicator Register (I2CSHIR) |     |

| 24.4.7 I2C Slave SDA Hold Time Register (I2CSHT)              |     |

| 24.4.8 I2C Data Register (I2CD)                               |     |

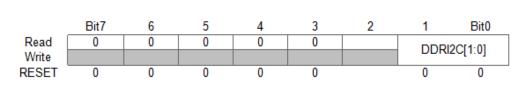

| 24.4.9 I2C Port Direction Register (I2CDDR)                   |     |

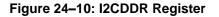

| 24.4.10 I2C Port Data Register (I2CPDR)                       |     |

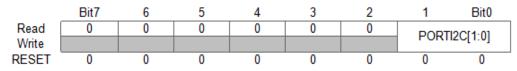

| 24.5 Functional Description                                   | 239 |

| 24.5.1 Master Mode                                            |     |

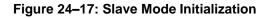

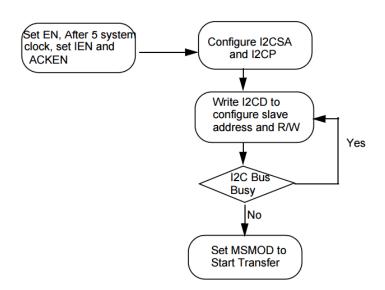

| 24.5.2 Slave Mode                                             |     |

| 24.5.3 Protocol                                               |     |

| 24.5.4 Arbitration Procedure                                  |     |

| 24.5.5 Clock Synchronization                                  |     |

| 24.5.6 Handshaking                                            |     |

| 24.5.7 Clock Stretching                                       |     |

| 24.5.8 High-Speed Mode Operation                              |     |

| 24.5.9 Software Transaction Flow Diagrams                     |     |

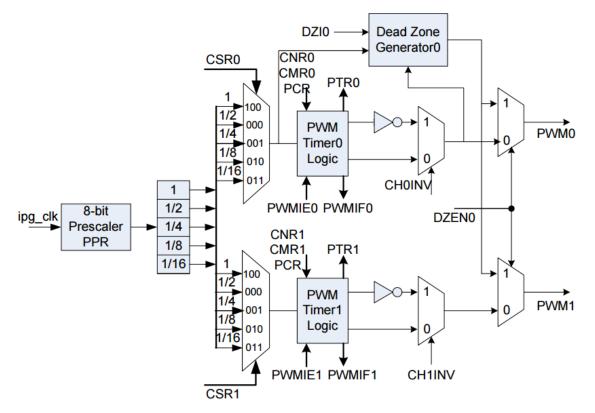

| 25. Pulse Width Modulator (PWM)                               |     |

| 25.1 Introduction                                             |     |

| 25.2 Features                                                 |     |

| 25.3 Block Diagram                                            |     |

| 25.4 Signal Description                                       |     |

| 25.5 Memory Map and Registers                                 |     |

| 25.5.1 Memory Map                                             |     |

| 25.5.2 Registers                                              |     |

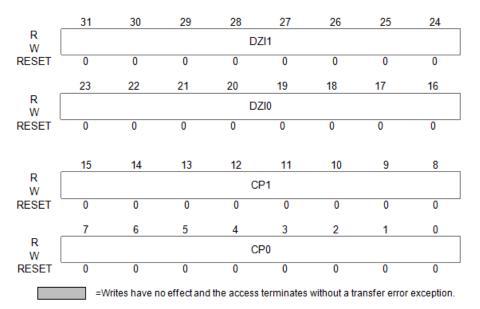

| 25.5.2.1 PWM Pre-Scale Register (PPR)                         |     |

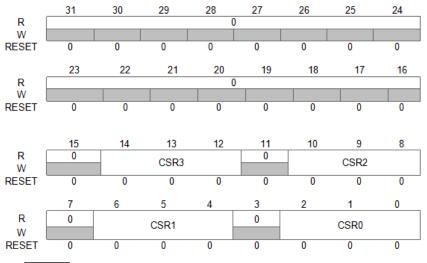

| 25.5.2.2 PWM Clock Select Register (PCSR)                     |     |

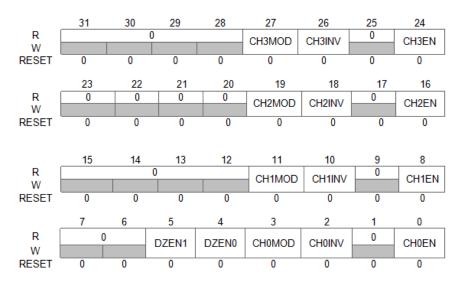

| 25.5.2.3 PWM Control Register (PCR)                           |     |

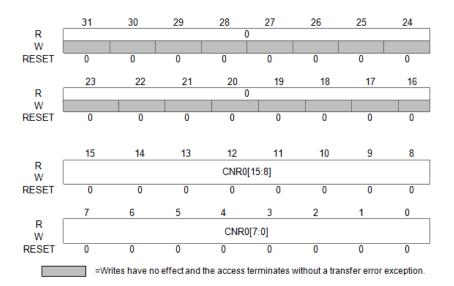

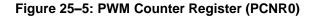

| 25.5.2.4 PWM Counter Register (PCNR0/1/2/3)                   |     |

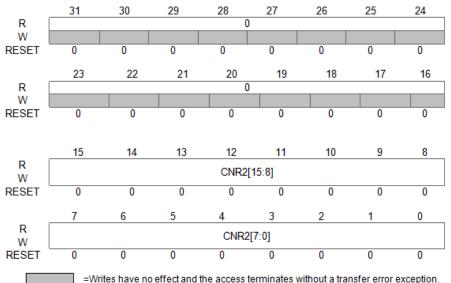

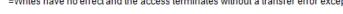

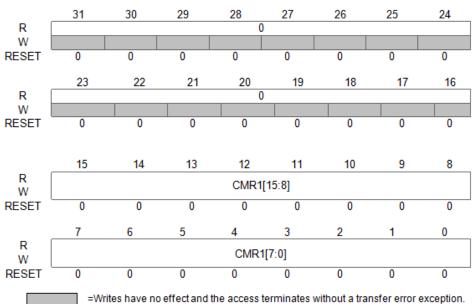

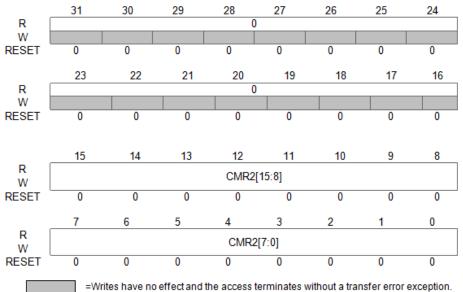

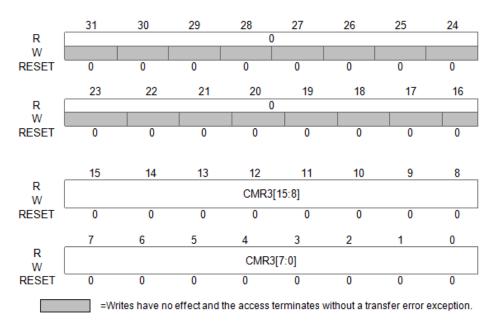

| 25.5.2.5 PWM Comparator Register (PCMR0/1/2/3)                |     |

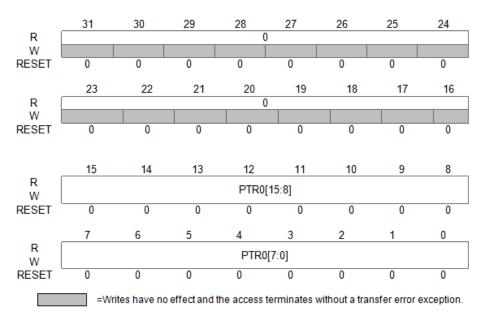

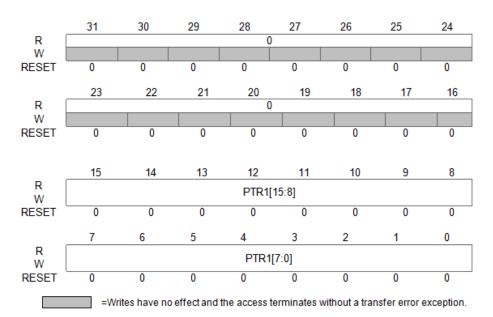

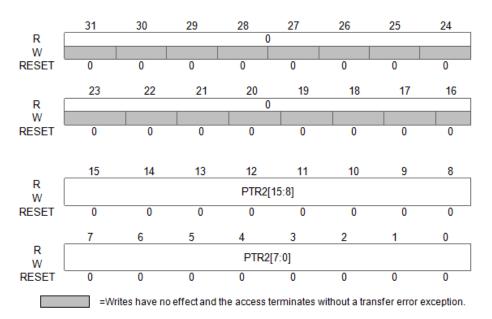

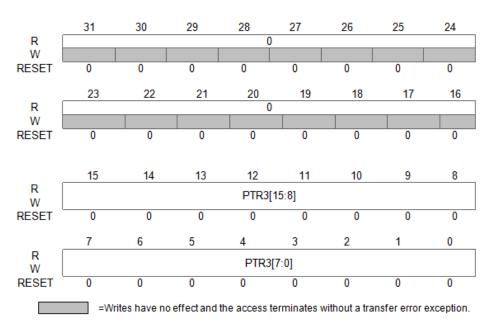

| 25.5.2.6 PWM Timer Register (PTR0/1/2/3)                      |     |

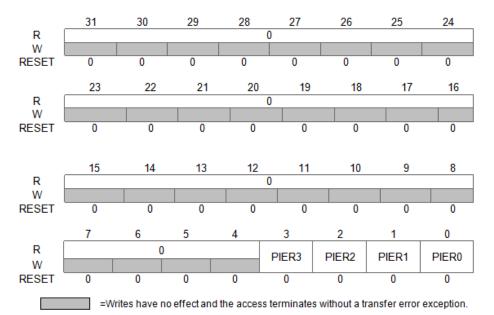

| 25.5.2.7 PWM Interrupt Enable Register (PIER)                 |     |

|                                                               |     |

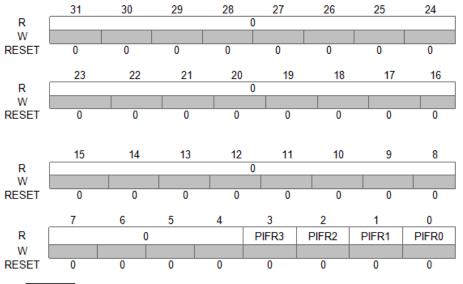

|     | 25.5.2.8 PWM Interrupt Flag Register (PIFR)                 |     |

|-----|-------------------------------------------------------------|-----|

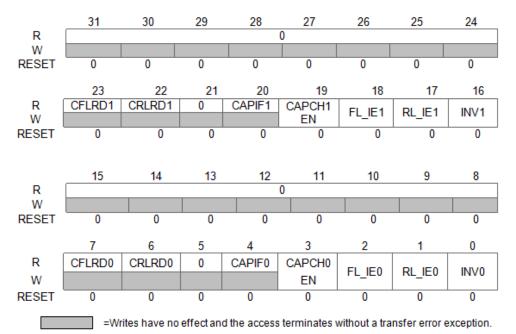

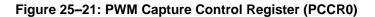

|     | 25.5.2.9 PWM Capture Control Register (PCCR0/1)             |     |

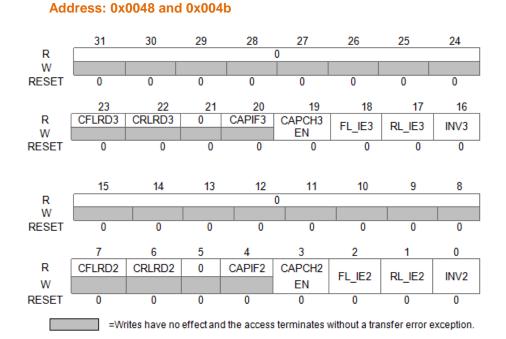

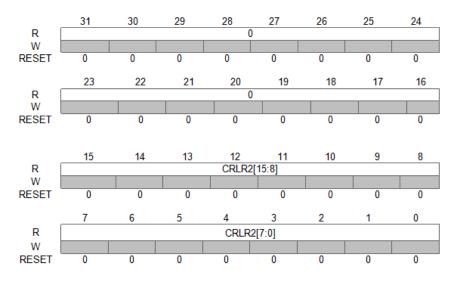

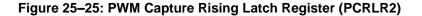

|     | 25.5.2.10 PWM Capture Rising Latch Register (PCRLR0/1/2/3)  |     |

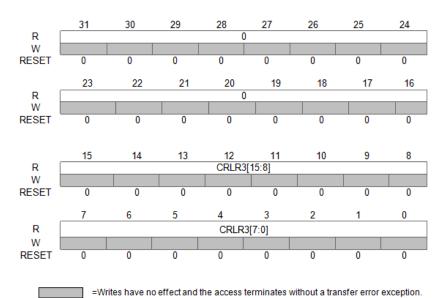

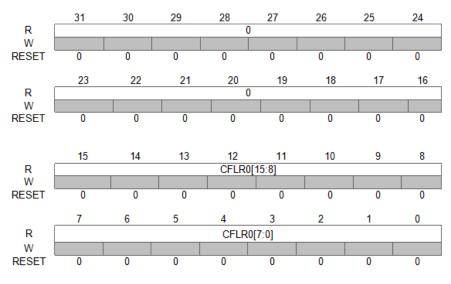

|     | 25.5.2.11 PWM Capture Falling Latch Register (PCFLR0/1/2/3) |     |

|     | 25.5.2.12 PWM Port Control Register (PPCR)                  |     |

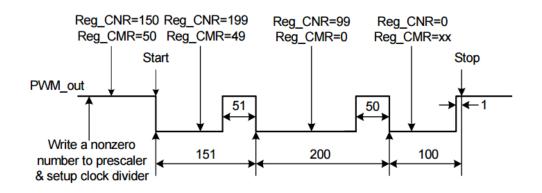

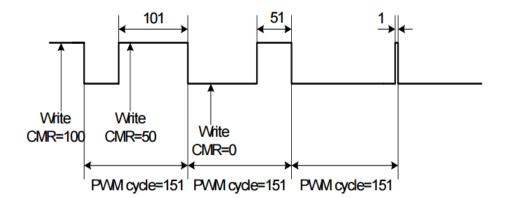

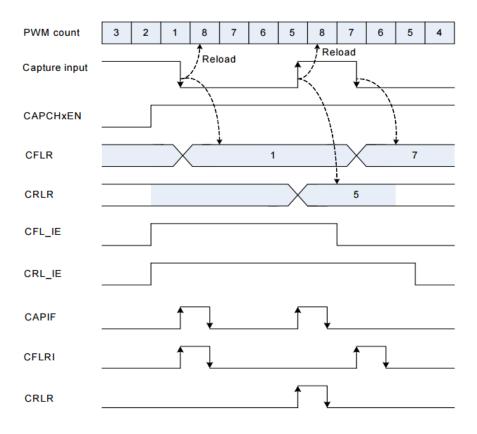

|     | 25.6 Functional Descriptions                                | 269 |

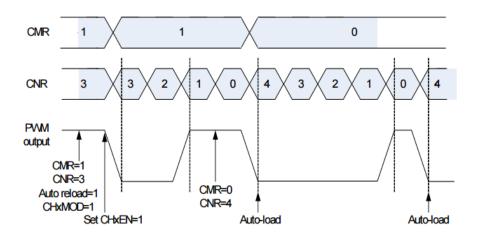

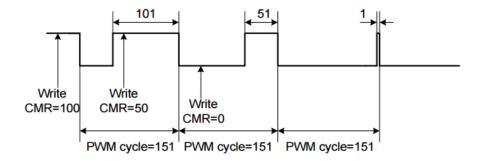

|     | 25.6.1 PWM Double Buffering and Automatic Reload            |     |

|     | 25.6.2 Modulate Duty Ratio                                  |     |

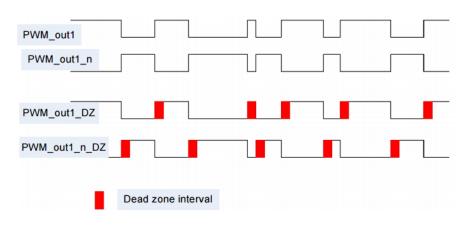

|     | 25.6.3 Dead-Zone Generator                                  | 270 |

|     | 25.6.4 PWM Timer Start Procedure                            |     |

|     | 25.6.5 PWM Timer Stop Procedure                             |     |

|     | 25.6.6 Capture Start Procedure                              |     |

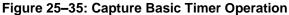

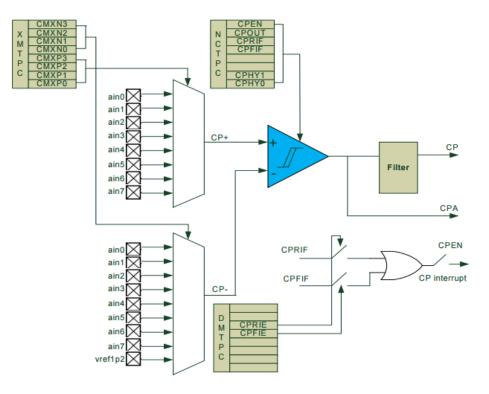

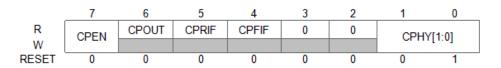

|     | 25.6.7 Capture Basic Timer Operation                        |     |

| 26. | Comparator Modules (COMP)                                   |     |

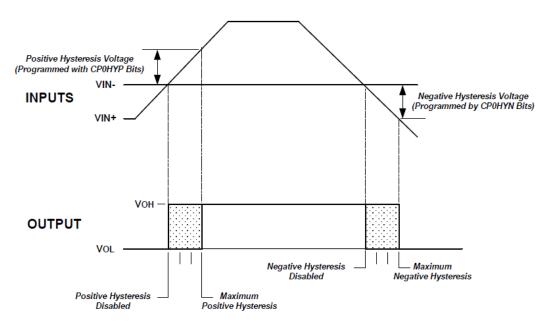

|     | 26.1 Introduction                                           | 272 |

|     | 26.2 Block Diagram                                          | 272 |

|     | 26.3 Modes of Operation                                     | 273 |

|     | 26.3.1 Wait Mode                                            |     |

|     | 26.3.2 Doze Mode                                            |     |

|     | 26.3.3 Stop Mode                                            |     |

|     | 26.4 Memory Map and Registers                               | 274 |

|     | 26.4.1 Memory Map (Base: 0x400a_0000, 0x400b_0000)          | 274 |

|     | 26.4.2 Registers                                            | 274 |

|     | 26.4.2.1 Comparator Control Register                        |     |

|     | 26.4.2.2 Comparator Mode Selection Register                 |     |

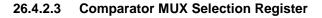

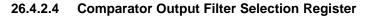

|     | 26.4.2.3 Comparator MUX Selection Register                  |     |

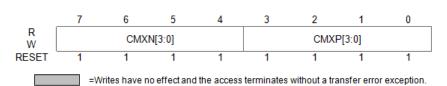

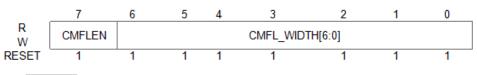

|     | 26.4.2.4 Comparator Output Filter Selection Register        |     |

|     | 26.5 Function Description                                   | 278 |

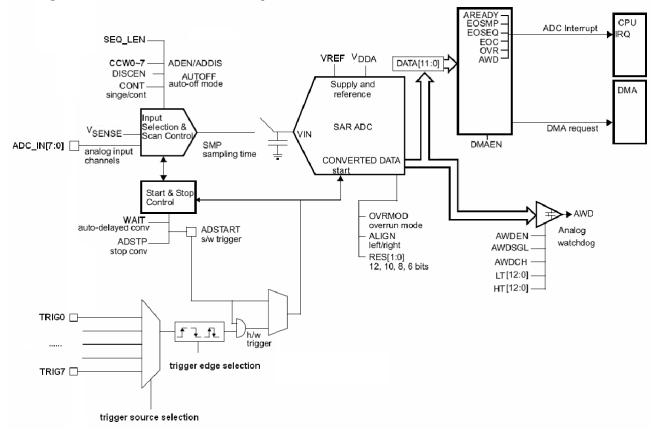

| 27. | Analog-to-Digital Converter (ADC)                           |     |

|     | 27.1 Introduction                                           | 279 |

|     | 27.2 ADC Main Features                                      | 279 |

|     | 27.3 ADC Functional Description                             |     |

|     | 27.3.1 ADC On-Off Control (ADEN, ADDIS, ADRDY)              |     |

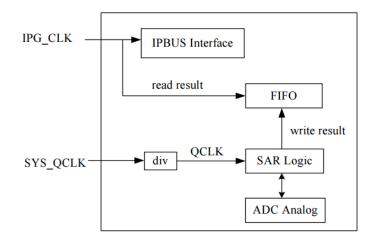

|     | 27.3.2 ADC Clock                                            |     |

|     | 27.3.3 Configuring the ADC                                  |     |

|     | 27.3.4 Channel Selection (CCWi)                             |     |

|     | 27.3.5 Programmable Sampling Time (SMP)                     |     |

|     |                                                             |     |

|     | 27.3.6 Single Conversion Mode (CONT=0) |                                                       |           |  |  |

|-----|----------------------------------------|-------------------------------------------------------|-----------|--|--|

|     | 27.3.7 Continuou                       | s Conversion Mode (CONT=1)                            |           |  |  |

|     | 27.3.8 Starting Co                     | onversions (ADSTART)                                  |           |  |  |

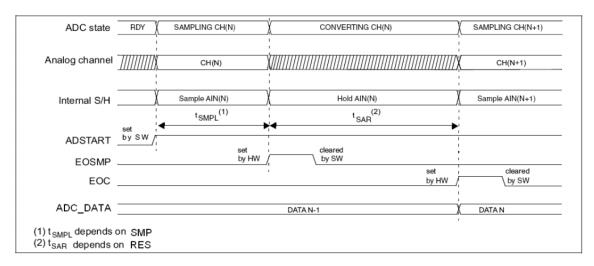

|     | 27.3.9 Timings                         |                                                       | 285       |  |  |

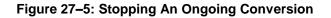

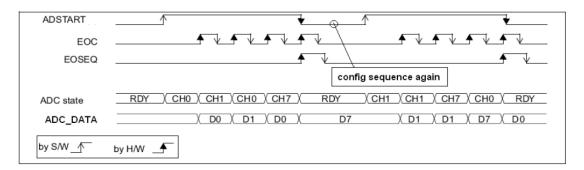

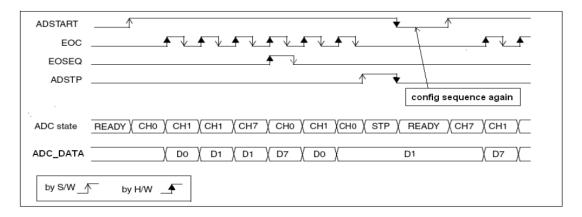

|     | 27.3.10 Stopp                          | ping An Ongoing Conversion (ADSTP)                    | 285       |  |  |

|     | 27.4 Conversion (                      | On External Trigger and Trigger Polarity              |           |  |  |

|     | 27.4.1 Discontinu                      | ous Mode (DISCEN)                                     |           |  |  |

|     | 27.4.2 Programm                        | able Resolution (RES) - Fast Conversion Mode          | 287       |  |  |

|     | 27.4.3 End of Cor                      | nversion, End of Sampling Phase (EOC, EOSMP Flags)    | 287       |  |  |

|     | 27.4.4 End of Cor                      | nversion Sequence (EOSEQ Flag)                        |           |  |  |

|     | 27.4.5 Example T                       | iming Diagrams                                        |           |  |  |

|     | 27.5 Data manage                       | ement                                                 |           |  |  |

|     | 27.5.1 Data FIFO                       | & Data Alignment (ADC_FIFO, ALIGN)                    | 290       |  |  |

|     | 27.5.2 ADC Overi                       | un (OVR, OVRMOD)                                      | 291       |  |  |

|     | 27.5.3 Managing                        | A Sequence of Data Converted Without Using The DMA    | 291       |  |  |

|     | 27.5.4 Managing                        | Converted Data Without Using The DMA Without Overrun  | 291       |  |  |

|     | 27.5.5 Managing                        | Converted Data Using DMA                              |           |  |  |

|     | 27.6 Low Power Features                |                                                       | 292       |  |  |

|     | 27.6.1 Wait Mode Conversion            |                                                       |           |  |  |

|     | 27.6.2 Auto-Off Mode (AUTOFF)          |                                                       | 292       |  |  |

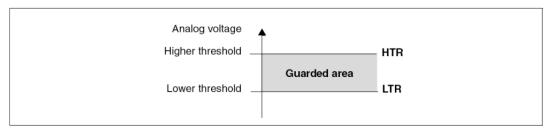

|     | 27.7 Analog Window Watchdog            |                                                       |           |  |  |

|     | 27.8 Temperature Sensor                |                                                       |           |  |  |

|     | 27.9 ADC Interrupts                    |                                                       |           |  |  |

|     |                                        | p and Registers                                       |           |  |  |

|     | -                                      | ory Map (Base: 0x4011 0000)                           |           |  |  |

|     |                                        | ters                                                  |           |  |  |

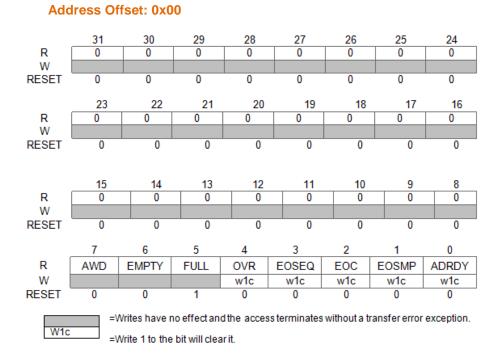

|     | 27.10.2.1                              | ADC Interrupt and Status Register (ADC_ISR)           |           |  |  |

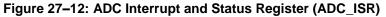

|     | 27.10.2.2                              | ADC Interrupt Enable Register (ADC_IER)               |           |  |  |

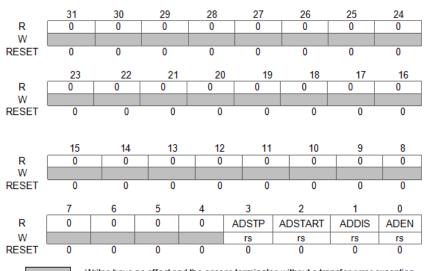

|     | 27.10.2.3                              | ADC Control Register (ADC_CR)                         | 298       |  |  |

|     | 27.10.2.4                              | ADC Configuration Register 1 (ADC_CFGR1)              | 300       |  |  |

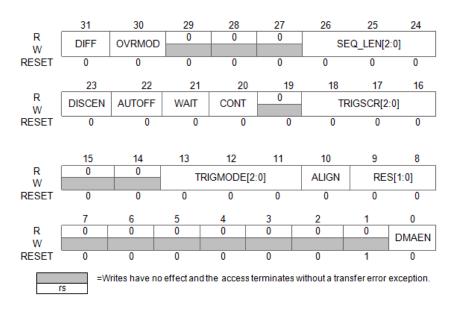

|     | 27.10.2.5                              | ADC Configuration Register 2 (ADC_CFGR2)              | 301       |  |  |

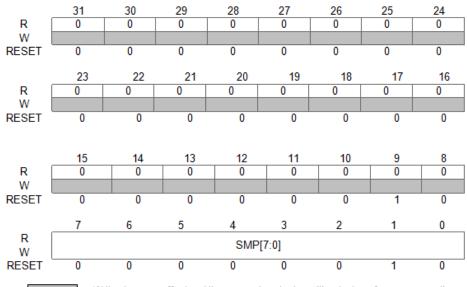

|     | 27.10.2.6                              | ADC Sampling Time Register (ADC_SMPR)                 | 302       |  |  |

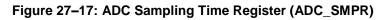

|     | 27.10.2.7                              | ADC Watchdog Register (ADC_WDG)                       | 303       |  |  |

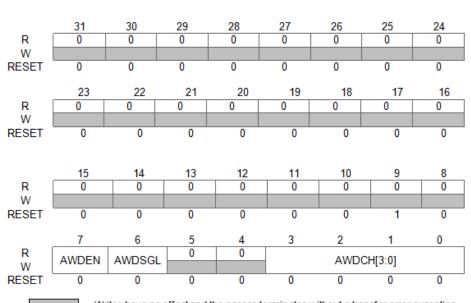

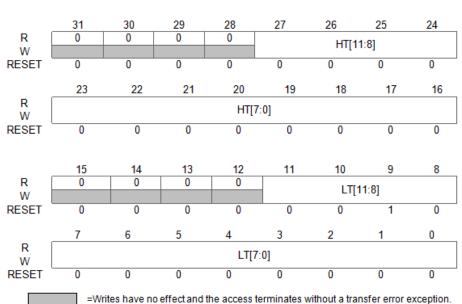

|     | 27.10.2.8                              | ADC Watchdog Threshold Register (ADC_TR)              | 304       |  |  |

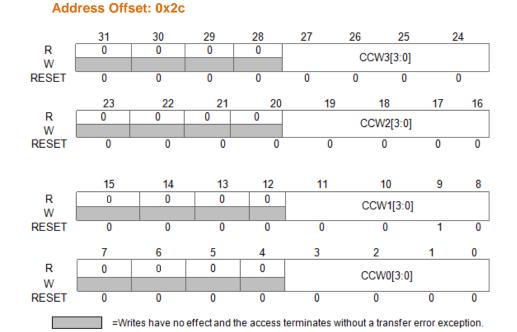

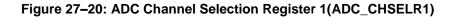

|     | 27.10.2.9                              | ADC Channel Selection Register (ADC_CHSELR1, ADC_CHSE | ELR2) 305 |  |  |

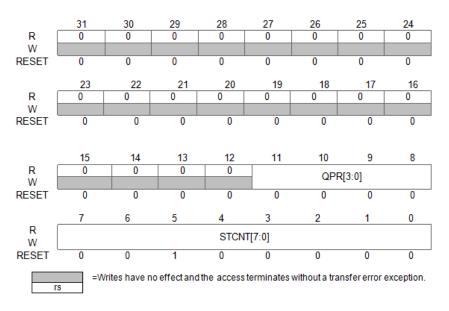

|     | 27.10.2.10                             | ADC FIFO Access Register (ADC_FIFO)                   |           |  |  |

| 28. | Mechanical Spe                         | cifications                                           | 307       |  |  |

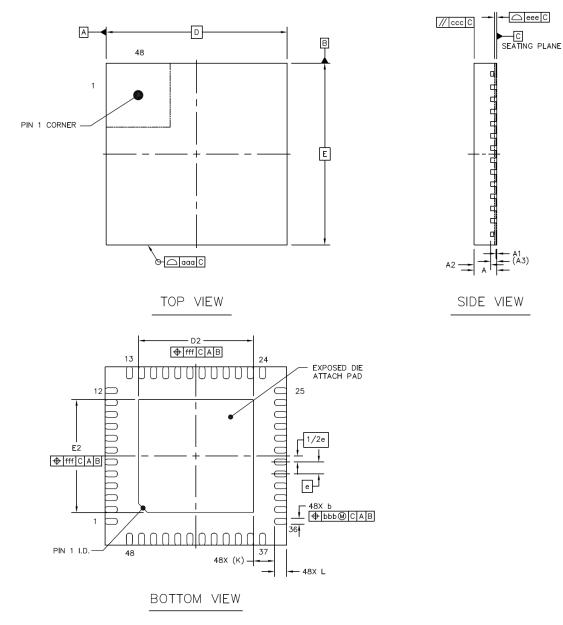

|     | 28.1 LT32U02(QF                        | N48) Mechanical Drawing                               |           |  |  |

# **TLT32U02/32A02**

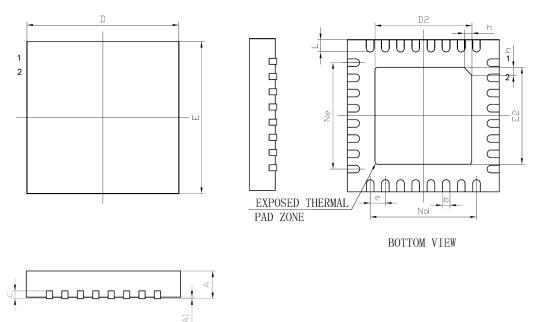

|     | 28.2 LT32A02(QFN32) Mechanical Drawing | 309 |

|-----|----------------------------------------|-----|

| 29. | Absolute Maximum Ratings               | 310 |

| 30. | DC Electrical Specifications           | 310 |

| 31. | Revision                               | 312 |

| 32. | Copyright                              | 312 |

# High Performance 32bit Micro Controller

# 1. Introduction

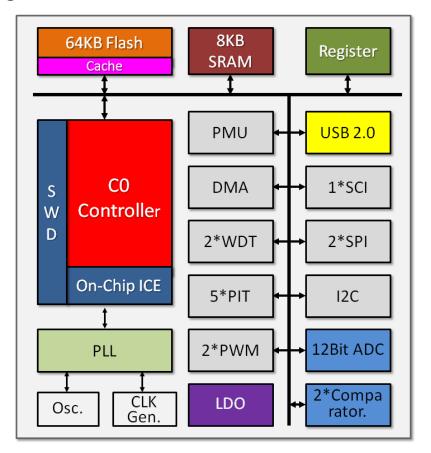

The LT32x02 incorporates the High-performance C0 32-bit RISC core operating at a 72MHz maximum frequency with high-speed embedded Flash memories (Flash up to 64Kbytes which contains an 1kbytes two-way set associative read Cache and SRAM up to 8Kbytes), and an extensive range of enhanced peripherals and I/Os. All devices offer standard communication interfaces, including two Master SPI, one I2C, and one UART. The LT32U02 also provide one USB2.0 Fast Speed controller. Both of LT3202 support up to four General-purpose 16-bit one eight timers. embedded programmable 24-bit timers, advanced-control PWM timers and two asynchronous Watch Dog Timers. It also provides Analog modules including one 1MSPS ADC with 8-channels and two Comparators.

The LT32U02 is QFN-48pin package, LT32A02 is QFN-32pin package. The operation temperature range is -40°C to 85°C and the operating voltage is 2.0/2.8V~5.5V.

# 2. Pin Assignment

Figure 2–2: LT32A02 Pin Assignment

# 3. Features

#### C0 Processor

- \_ 32-bit Load/Store Reduced Instruction set Computer (RISC) Architecture with fixed 16-bit Instruction Length

- \_ 16 Entry 32-bit General-Purpose Register File

- \_ Efficient 3-Stage Execution Pipeline, Hidden from Application Software

- \_ Single-cycle Instruction Execution for many Instructions, Three Cycles for Branches

- \_ Support for Byte / Half-word / Word Memory Accesses

- \_ Embedded Interrupt Controller, support Nested Vector Interrupts.

- \_ Single-cycle 32-bit x 32-bit Hardware Integer Multiplier Array

- \_ 3~13 Cycles Hardware Integer Divider Array

### 8K Bytes of Static Random-Access Memory (SRAM)

\_ Single Cycle Byte, Half-word (16-bit), and Word (32-bit) Reads and Writes

### 64K Bytes Embedded Flash (EFLASH)

- \_ Page Erase Capability: 512 bytes per Page

- \_ Read Cycle Time: 40ns (min)

- \_ Endurance: 100000 Cycles (min)

- \_ Greater than 20 Years Data Retention

- \_ Fast Page Erase/ Byte Program

- Half-word Program Time: 7.5us (max)

- Page Erase Time: 5ms (max)

- Mass Erase Time: 40ms (max)

- \_ Single Cycle Byte, Half-word (16-bit) and Word (32-bit) Read Access.

#### Reset

- \_ Internal power on reset circuit

- \_ Five sources of reset:

- Power-on Reset

- External Pin

- Software Reset

- Watchdog Timer

- Program Voltage Detect Reset

- \_ Status Flag Indicates Source of Last Reset

### Four Periodic Interval Timer

- \_ 16-bit Counter with Modulus "initial count" Register

- \_ Selectable as Free Running or Count down

- \_ 16 Selectable Prescalars  $\rightarrow$  2<sup>0</sup> to 2<sup>15</sup>

### Two Watchdog Timer

- \_ 16-bit Counter with Modulus "Initial Count" Register

- Pause Option for Low-power Modes

- \_ Up to 2000ms Service Time

### Two External Interrupts Port (EPORT)

- \_ Eight Channels for Each EPORT

- \_ Rising/falling Edge Select

- \_ Low/High-Level Sensitive

- \_ Interrupt Pins Configurable as General-purpose I/O

#### **Two Serial Peripheral Interface Master Module (SPI)**

- \_ SPI Master Mode

- \_ Shared SPICLK Ports

- \_ Two 4 Entries deep Read FIFO

- \_ Two 4 Entries deep Write FIFO

- Interrupt Generation after 1, 2, 3, or 4 Transferred Bytes

- \_ MSB/LSB Selectable

- \_ Variable Baud-rate During Communication

- \_ Serial Clock with Programmable Polarity and Phase

- \_ 16/32 bit Transmit/Receive Data Width

- \_ Byte Re-order

- \_ Controllable Slave Select (spiss0/1) bit

#### One Serial Communications Interface Module (SCI)

- \_ Standard Mark/Space Non-Return-to-Zero (NRZ) format

- The Baud Rate Divisor is a 22-bit Number Consisting of 16-bit Integer and 6-bit Fractional Part

- \_ Programmable 7-bit, 8-bit or 9-bit Data Format

- \_ Separately enabled Transmitter and Receiver

- \_ Separate Receiver and Transmitter Central Processor unit (CPU) Interrupt Requests

- \_ Programmable Transmitter Output Polarity

- \_ Two Receiver Wakeup Methods:

- Idle Line Wakeup

- Address Mark Wakeup

- \_ Interrupt-driven Operation with Eight Flags:

- Transmitter Empty

- Transmission Complete

- Receiver Full

- Idle receiver Input

- Receiver Overrun

- Noise Error

- Framing Error

- Parity Error

- \_ Receiver Framing Error Detection

- \_ Hardware Parity Checking

- \_ 1/16 bit-time Noise Detection

- \_ General-purpose, I/O Capability

- \_ Serial IR Interface Low-speed, IrDA-Compatible (up to 115.2Kbit/s)

### One USB2.0 Full Speed Compatible Device (LT32U02 Only)

- \_ Supports Internal Reference Clock or External 12MHz Crystal Reference Clock

- \_ Compliant with USB2.0 Full Speed Specification with on-chip Integrated PHY Module

- \_ Supports FS (12Mbps) Mode

- \_ Up to 8 Endpoints Supported Including Endpoint 0

- \_ All Endpoints except Endpoint 0 can support Interrupt and Bulk Transfer

- \_ All Endpoints except Endpoint 0 can be Configured as 8, 16, 32, 64 bytes FIFO size

- \_ Endpoint 0 Support Control Transfer

### **Two Pulse Width Modulator (PWM)**

- \_ Four Channel each PWM Controller

- \_ Programmable Period

- Programmable Duty Cycle

- \_ Two Dead-Zone Generator

- \_ Capture Function

- \_ Pins can be Configured as General-purpose I/O

#### ADC with 8-Channel

- \_ High Performance

- 12-bit, 10-bit, 8-bit or 6-bit configurable resolution

- ADC Conversion Time: 1.0µs for 12-bit Resolution (1 MHz), 0.88µs Conversion Time for 10 bit Resolution, Faster Conversion times can be obtained by Lowering Resolution.

- Programmable Sampling Time

- Data Alignment with Built-in Data Coherency

- DMA Support

- \_ Low Power

- Application cans Reduce PLCK Frequency for Low Power Operation while still Keeping Optimum ADC Performance. For Example, 1.0µs Conversion Time is kept, whatever the Frequency of PCLK.

- Wait mode: Prevents ADC Overrun in Applications with Low Frequency PLCK

- Auto off mode: ADC is Automatically Powered Off Except during the Active Conversion phase. This Dramatically Reduces the Power Consumption of the ADC.

- \_ Analog Input Channels

- 8 External Analog Inputs

- 1 Channel for Internal Reference Voltage

- 1 Channel for Internal Temperature Sensor

- \_ Start-of-Conversion can be Initiated:

- By Software

- By Hardware Triggers with Configurable Polarity

- \_ Conversion Modes

- Can Convert a Single Channel or can Scan a Sequence of Channels.

- Single Mode Converts Selected Inputs once per Trigger

- Continuous Mode Converts Selected Inputs Continuously

- Discontinuous Mode

- \_ Interrupt Generation at the end of Sampling, end of Conversion, end of Sequence Conversion, and in case of Analog Watchdog or Overrun Events.

- \_ Analog Watchdog

- Single-ended and Differential-input Configurations

- Converter uses an Internal Reference or an External Reference

### Two Analog Comparators

- \_ Programmable Response Time

- \_ Programmable Hysteresis

- \_ Support Analog input Multiplexer with Nine Selection

- \_ Two Optional Outputs: Filtered or Asynchronous Output

- \_ Selectable Rising/Falling Edge Interrupt

#### ■ PMU

- \_ Support 3.3V LDO (for USB PHY Power Supply) with Maximum Load Current 100mA

- \_ 3.3V LDO Support Power Down for Save Power Consumption

- \_ Support 1.5V LDO with Maximum Load Current 50mA

- 1.5V LDO Support Four Mode: Normal, Lower power, High power

#### Programmable Voltage Detector

**TLT32U02/32A02**

#### Internal Oscillator

- \_ 128KHz Oscillator Clock for Watchdog and PMU

- \_ 72MHz Oscillator Clock which can be used for System Clock

- \_ 48MHz USBPLL Clock which can be used for System Clock

#### External Crystal Oscillator

- \_ Up to 20Mhz External Crystal Oscillator Clock which can be used for System Clock

- \_ 32.768Khz External Crystal Oscillator Clock which can be used for Watchdog

### 4. Block Diagram

Figure 4–1: LT32U02 Block Diagram

# 5. Signal Properties Summary

| Name            | Alternate | Qty. | Dir.   | Input Sync | Pullup <sup>1</sup> | Output Drive<br>(ST/OD/SP) <sup>2</sup> |  |

|-----------------|-----------|------|--------|------------|---------------------|-----------------------------------------|--|

| SCI (2)         |           |      |        |            |                     |                                         |  |

| RXD0            |           | 1    | I/O    | Ν          | Pull-up             | ST                                      |  |

| TXD0            |           | 1    | I/O    | Ν          | Pull-up             | ST                                      |  |

| USB (2)         |           |      |        |            |                     |                                         |  |

| DP              |           | 1    | Analog |            |                     | SP                                      |  |

| DM              |           | 1    | Analog |            |                     | SP                                      |  |

| I2C (2)         | -         |      |        |            |                     |                                         |  |

| SCL             |           | 1    | I/O    | Ν          | Pull-up             | OD                                      |  |

| SDA             |           | 1    | I/O    | Ν          | Pull-up             | OD                                      |  |

| SPI (7)         | -         |      |        |            |                     |                                         |  |

| MSS0            |           | 1    | I/O    | Ν          | -                   | ST                                      |  |

| MSDI0           |           | 1    | I/O    | Ν          | Pull-up             | ST                                      |  |

| MSDO0           |           | 1    | I/O    | Ν          | -                   | ST                                      |  |

| MSS1            |           | 1    | I/O    | Ν          | -                   | ST                                      |  |

| MSDI1           |           | 1    | I/O    | Ν          | Pull-up             | ST                                      |  |

| MSDO1           |           | 1    | I/O    | Ν          | -                   | ST                                      |  |

| MSCK            |           | 1    | I/O    | Ν          | -                   | ST                                      |  |

| <b>PWM0 (4)</b> |           |      |        |            |                     |                                         |  |

| PWM0[0]         |           | 1    | I/O    | Ν          | Pull-up             | ST                                      |  |

| PWM0[1]         |           | 1    | I/O    | Ν          | Pull-up             | ST                                      |  |

| PWM0[2]         |           | 1    | I/O    | Ν          | Pull-up             | ST                                      |  |

| PWM0[3]         |           | 1    | I/O    | Ν          | Pull-up             | ST                                      |  |

| PWM1 (2)        |           |      |        |            |                     |                                         |  |

| PWM1[0]         |           | 1    | I/O    | Ν          | Pull-up             | ST                                      |  |

| PWM1[1]         |           | 1    | I/O    | Ν          | Pull-up             | ST                                      |  |

| PWM1[2]         |           | 1    | I/O    | Ν          | Pull-up             | ST                                      |  |

| PWM1[3]         |           | 1    | I/O    | Ν          | Pull-up             | ST                                      |  |

| ADC (7)         |           |      |        |            |                     |                                         |  |

| AIN[7:3]        | INT0[7:3] | 5    | Mixed  | Ν          | -                   | -                                       |  |

| AIN[1:0]        | -         | 2    | Analog | Ν          | -                   | -                                       |  |

Table 5–1: Signal Properties Summary

| Name            | Alternate | Qty. | Dir. | Input Sync | Pullup <sup>1</sup> | Output Drive<br>(ST/OD/SP) <sup>2</sup> |  |

|-----------------|-----------|------|------|------------|---------------------|-----------------------------------------|--|

| Edge Port 0 (1) |           |      |      |            |                     |                                         |  |

| INT0[1]         | -         | 1    | I/O  | Ν          | Pull-up             | ST                                      |  |

| Edge Port 0 (   | (5)       |      |      |            |                     |                                         |  |

| INT1[1]         |           | 1    | I/O  | Ν          | Pull-up             | ST                                      |  |

| INT1[2]         | 32K_XO    | 1    | I/O  | Ν          | Pull-up             | ST                                      |  |

| INT1[3]         | 32K_XI    | 1    | I/O  | Ν          | Pull-up             | ST                                      |  |

| INT1[4]         |           | 1    | I/O  | Ν          | Pull-up             | ST                                      |  |

| INT1[5]         |           | 1    | I/O  | Ν          | Pull-up             | ST                                      |  |

| Debug Port (    | 2)        |      |      |            |                     |                                         |  |

| SWDIO           | AIN[2]    | 1    | I/O  | Ν          | Pull-up             | ST                                      |  |

| SWDCK           | INT0[0]   | 1    | I/O  | Ν          | Pull-up             | ST                                      |  |

| Clock (3)       |           |      |      |            |                     |                                         |  |

| EXTAL           | INT0[2]   | 1    | I/O  | Ν          | -                   | SP                                      |  |

| XTAL            | INT1[7]   | 1    | I/O  | Ν          | -                   | SP                                      |  |

| CLKOUT          | INT1[0]   | 1    | I/O  | Ν          | Pull-up             | ST                                      |  |

| RESET (2)       |           |      |      |            |                     |                                         |  |

| RESETB          | -         | 1    | -    | Y          | -                   | SP                                      |  |

| RSTOUT          | INT1[6]   | 1    | I/O  | Ν          | Pull-up             | ST                                      |  |

| Power Suppl     | у         |      |      |            |                     |                                         |  |

| VDDH            | -         | -    | -    | -          | -                   | SP                                      |  |

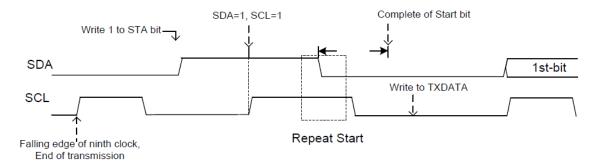

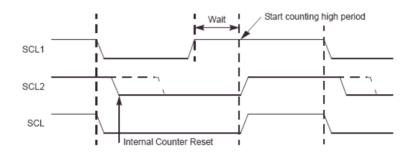

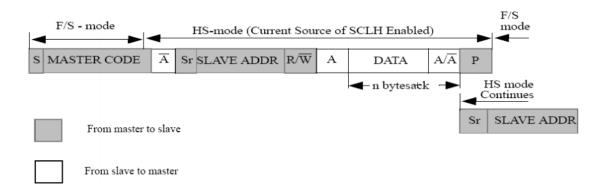

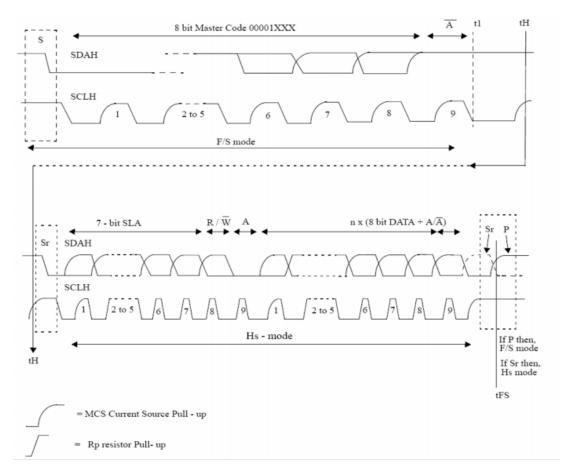

| VDDH1           | -         | -    | -    | -          | -                   | SP                                      |  |